- 06

- Oct

Verminder die aantal komponente en verminder die oppervlakte van die printplaat deur draadlose RF -integrasie

Verminder die aantal komponente en verminder die oppervlakte van circuit board deur draadlose RF -integrasie

In vandag se draadlose toestelle is meer as die helfte van die komponente op die printplaat analoog RF -toestelle. ‘N Doeltreffende manier om die oppervlakte van die printplaat en die kragverbruik te verminder, is om meer grootskaalse RF-integrasie uit te voer en te ontwikkel na ‘n chip op stelselvlak. Hierdie artikel stel die ontwikkelingstatus van RF -integrasie bekend en stel ‘n paar teenmaatreëls en oplossings vir sommige van hierdie probleme voor.

‘N Paar jaar gelede is die selfoonmark oorheers deur enkelband- en dubbelband-enkelmodusse, en die tegnologie wat gebruik is, is slegs ??? Hou in totaal een of twee sellulêre bande ??? Dieselfde modulasiemetode, multi-kanaal toegangskema en protokol word in die houfrekwensieband aangeneem. Daarteenoor is die ontwerp van vandag se nuwe generasie selfone baie ingewikkelder en kan dit multi-band en multi-mode bied ??? Dit het ‘n persoonlike netwerk van Bluetooth, GPS -posisionering en ander funksies, en UWB- en TV -ontvangsfunksies het begin verskyn. Boonop het toepassings soos speletjies, beelde, klank en video baie algemeen in selfone geword.

‘N Draadlose telefoon word ‘n ingewikkelde toestel met die naam persoonlike persoonlike vermaaklikheidsentrum. Die ontwikkelingstendens bied steeds meer uitdagings aan ontwerpers. Hoewel die nuwe generasie selfone in vergelyking met selfone met slegs stemfunksie aansienlik toegeneem het in kommunikasieverwerking, toepassingsverwerking, die aantal RF -koppelvlakke en geïntegreerde geheuevermoë, verwag gebruikers steeds dat selfone kleiner volume, vaartbelynde vorm, laag prys en groot kleurskerm, dit kan bystand en gesprekstyd bied, soortgelyk aan tradisionele stemfone. Deur die bestaande algehele grootte en kragverbruik te behou, maar die funksie eksponensieel te laat toeneem, terwyl die totale stelselkoste onveranderd bly, bied dit baie probleme vir die stelselontwerpers.

Dit is duidelik dat die probleem alle dele van die hele stelselontwerp behels, sowel as die verskaffers van alle draadlose kommunikasie- en vermaaklikheidsinhoud. Een gebied wat veral effektief is in die vermindering van die oppervlakte van die bord en die kragverbruik, is die RF -deel van die ontwerp van die draadlose stelsel. Dit is omdat in vandag se tipiese selfoon meer as die helfte van die komponente op die bord analoog RF-komponente is, wat saam 30-40% van die hele kaartoppervlak uitmaak, soos Bluetooth RF-stelsels soos GPS en WLAN ook baie verhoog die vereistes vir ruimte.

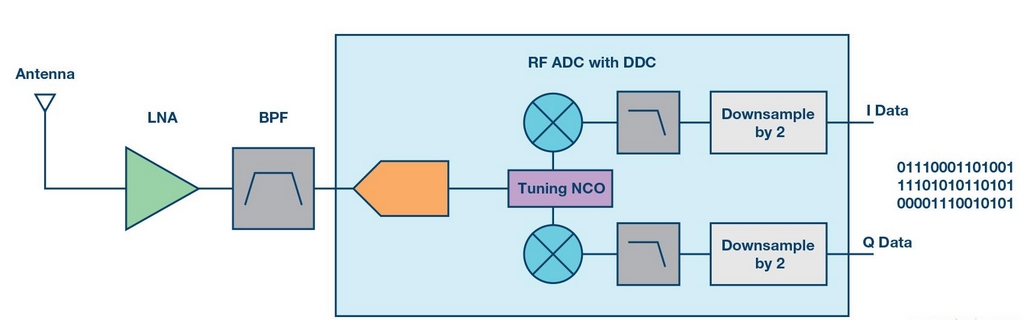

Die oplossing is om meer grootskaalse RF-integrasie uit te voer en uiteindelik te ontwikkel tot ‘n volledig geïntegreerde stelselvlak-chip. Sommige ontwerpers sit analoog-na-digitale omsetters in die antenna om die totale ruimte op die printplaat te verminder wat nodig is vir RF-funksies. As tegnologie vir halfgeleierintegrasie meer funksies in ‘n enkele toestel kan integreer, word die aantal diskrete toestelle en die ruimte op die printplaat wat gebruik word om hierdie toestelle te akkommodeer, dienooreenkomstig verminder. Namate die industrie na die integrasie van stelselmatige skyfies beweeg, sal ontwerpers voortgaan om nuwe tegnologieë te vind om die teenstrydigheid tussen ‘n hoër RF -kompleksiteit en ‘n langer batterylewe in klein draadlose toestelle te ontmoet.

Ontwikkelingstatus van RF -integrasie

Ongeveer twee jaar gelede het ‘n belangrike ontwikkeling van RF -integrasie verskyn. Op die oomblik het die ontwikkeling van RF -tegnologie en digitale basisbandmodem dit moontlik gemaak om superheterodyne RF -toestelle te vervang deur direkte omskakelingsontvangers in draadlose selfone. Superheterodyne RF -toestelle gebruik multistadige mengers, filters en veelvuldige spanningsgestuurde ossillators (VCO’s), wat al baie jare goed gebruik word, maar die integrasie van RF -toestelle met direkte frekwensie kan die totale aantal GSM RF -komponente aansienlik verminder. Aan die einde van die negentigerjare het ‘n tipiese enkelband superheterodyne RF -substelsel PA, antenneskakelaar, LDO, klein sein RF en vctcxo ingesluit, wat ongeveer 1990 aparte toestelle benodig; Vandag kan ons ‘n direkte frekwensie -omskakelingstelsel ontwerp met ‘n vierbandfunksie, wat VCO-, VCXO- en PLL -lusfilter integreer, maar die aantal komponente daarvan is minder as 200. Figuur 50: vierbands GSM -ontvanger met hoë integrasie.

Die transceiver trf6151 (Figuur 1) van Texas Instruments for GSM bevat byvoorbeeld ‘n spanningsreguleerder op die chip, VCO- en VCO-kanaal, PA-kragbeheer, PLL-lusfilterrandblokkering, stap-vir-stap beheer van LNA en VCXO.

Vir ontwerpers help gevorderde integrasie om ‘n paar groot probleme in draadlose RF te oorkom, waaronder die mees basiese een die GS -kragtoevoer en regulering van die sender is. Tydens ‘n oproep verander die batteryspanning met die verandering van temperatuur en tyd. Die geraaskoppeling van TX VCO en Rx VCO kragtoevoer sal ook die prestasie van die hele stelsel beïnvloed. Daarom word ontwerpers gekonfronteer met die probleem om die RF -kringbordreguleerder en die meeste verwante passiewe komponente op te los. Deur hierdie toestelle in die RF -transceiver te integreer, beteken dat die enigste eksterne komponent wat nodig is ‘n eenvoudige ontkoppelingskondensator is, wat direk aan die kragtoevoer gekoppel is, wat nie net die ontwerp vergemaklik nie, maar ook ruimte op die printplaat bespaar.

‘N Ander uitdaging vir RF -ontwerpers is die VCO -afstembereik en sluittyd. In alle analoog VCO -ontwerpe. Omdat dit dikwels nodig is om die sluittyd en die afstembereik te balanseer, word die lusfilter gewoonlik buite die chip geplaas. Soms kan dit opgelos word in die sagteware -beheer van die VCO -afstemreeks. Hierdie metode stel egter addisionele hulpbronvereistes voor vir die algehele ontwikkeling van telefoon. As die digitale afstemfunksie by die VCO ingesluit is en selfkalibrasie kan sorg, kan ‘n uitgebreide stembereik verkry word en kan die lusfilterelement in die chip geplaas word. Uiteraard kan hierdie skema ontwerpingenieurs in staat stel om hul werk te vereenvoudig.

Om die sender se kragbeheer te verkry wat deur die GSM -stelsel benodig word, bevat PA -vervaardigers hierdie funksie oor die algemeen in die kragversterkermodule (PAM). Die kragbeheerder bestaan gewoonlik uit tot duisende digitale CMOS -hekke, wat in ‘n onafhanklike chip in PAM vervaardig word. Hierdie element verhoog die koste van PAM met $ 0.30 ~ 0.40. Deur hierdie funksie in RF -toestelle te integreer, sal GaAs PAM -vervaardigers nie in staat wees om digitale CMOS -stroombane aan te skaf en in PAM te installeer nie. Vir ‘n OEM wat elke maand duisende produkte vervaardig, sal die verwydering van hierdie oortollige komponent hul koste aansienlik verminder.

‘N Ander gebied waar gevorderde integrasie aansienlike besparings kan meebring, is VCXO. In die verlede is duur vctcxo -modules gekoop en ontwerp in RF -toestelle as diskrete komponente. Om algemene komponente van vctcxo -modules in RF -toestelle op te neem, kan dus koste en verwante ontwerpprobleme verminder. Met behulp van trf6151 is slegs ‘n goedkoop kristal en varaktor nodig om die funksie van vctcxo te voltooi.

Ondanks hierdie integrasie en ontwerpvergemakliking, staan RF -ontwerpingenieurs steeds voor moeilike keuses, waarvan een insetgevoeligheid en Rx -kragverbruik is. Dit is algemeen bekend dat hoe groter die stroom wat gebruik word in die ontwerp van lae geraasversterker (LNA), hoe laer die algehele geraaskenmerke. Die ontwerpingenieur moet die totale kragbegroting van die ontvanger en die sensitiwiteitsvlakvereistes van die ontvanger bepaal. Die geraas neem egter nie af met die vermindering van krag nie. Eintlik is dit die teenoorgestelde. Hoewel dit aan die GSM -standaardspesifikasie kan voldoen, moet ontwerpers hulself dikwels afvra of dit die moeite werd is om die prys in kragverbruik te betaal om ‘n sekere sensitiwiteitsvlak te bereik. Hierdie vraag verduidelik ook waarom ontwerpingenieurs en vervaardigers van IC nodig is om nou saam te werk in die hele ontwerpproses. Die terugvoer van ontwerpingenieurs kan IC -vervaardigers lei om die draadlose industrie beter te bedien by die ontwikkeling van toekomstige RF -produkte.

Ontwikkel na SOC

Dit is baie belangrik om die koste, krag en kompleksiteit van draadlose stelsels te verminder om suksesvol aan die vereistes van stelselintegrasie te voldoen. Die ontwikkeling van hoëintegrasie -oplossings vir selfone vereis egter dat die halfgeleierbedryf komplekse tegniese struikelblokke moet oorkom. Sommige van hierdie struikelblokke is selde deur ontwerpers bekommerd, omdat baie van hulle nie wil weet hoe SOC -toestelle gemaak word nie, solank dit die vereiste prestasie kan lewer. Daarom is dit nodig om ‘n vinnige begrip te hê van sommige prosestegnologieë, wat die vermoë en beskikbaarheid van toestelle wat gebruik word vir die integrasie van selfone, sal beïnvloed.

Daar is verskeie uitvoerbare skemas vir die integrasie van die RF elektroniese stelsel vir selfone. Eerstens kan ‘n tradisionele RF -argitektuur geïmplementeer word in ‘n relatief eenvoudige bipolêre of BiCMOS -proses met behulp van tradisionele tegnologie. Die finale RF -chip kan saamgestel word met digitale logika -funksies vir selfone met behulp van multi -chip verpakkingstegnologie (stelselvlakverpakkingstegnologie). Alhoewel hierdie tegnologie baie voordele inhou, soos die gebruik van bekende RF -ontwerpmetodes en volwasse prosesse en tegnologieë, is dit moeilik om te kommersialiseer weens die hoë koste en opbrengs van toetsapparate.

Boonop kan die integrasie van die elektroniese stelsel vir selfone ook verkry word deur ‘n gevorderde BiCMOS (SiGe) waferproses. Omdat die verwerking van SiGe HBT -toestelle egter ‘n bykomende litografiese proses vereis, sal die finale skyfie ‘n ekstra koste vereis. Terselfdertyd, omdat SiGe BiCMOS -tegnologie nie die mees gevorderde litografieproses kan gebruik nie, bly BiCMOS -proses gewoonlik agter die gevorderde digitale CMOS -proses. Dit sal groot druk meebring om die eienskappe van selfone te verhoog en koste te verminder. Dit kan nie opgelos word met ‘n eenvoudige wafer -prosesstrategie nie, want hierdie tegnologie kan nie altyd die stelsellogika of digitale onderdeel teen die laagste moontlike prys hou nie. Daarom is monolitiese integrasie van die stelselbandbandfunksie RF -deel in BiCMOS (of SiGe) nie ‘n goeie keuse nie.

Die finale oplossing wat oorweeg kan word, is RF -integrasie in CMOS, wat ook groot uitdagings in die gesig staar. Alhoewel daar verskillende CMOS mobiele RF -ontwerpe is, is hierdie ontwerpe grotendeels gebaseer op analoogfunksies. Dit is moeilik om analoog -mengers, filters en versterkers met CMOS -tegnologie te implementeer, en die kragverbruik is oor die algemeen groter as die SiGe BiCMOS -skema. Met die ontwikkeling van prosesstegnologie, word die CMOS -vlak laer en laer, wat analoog ontwerp moeiliker maak. In die vroeë stadium van die ontwikkeling van nuwe prosesse kan toestelmodellering en prosesvolwassenheid in die algemeen nie voldoen aan die vereistes van hoë presisie parametermodellering wat nodig is vir analoog module-ontwerp nie. Die onlangs ontwikkelde digitale CMOS RF -argitektuur maak monolitiese CMOS -integrasie egter aantrekliker.

Hierdie oplossings dryf ook die halfgeleierbedryf aan, aangesien vervaardigers op soek is na goedkoop RF-stelselvlak-chipoplossings. Alhoewel elke integrasie -skema probleme ondervind, is dit inderdaad verbasend dat RF -komponentintegrasie so ‘n hoë vlak kan bereik. Om hierdie probleme te oorkom, sal ‘n groot stap vorentoe neem in die ontwerp van draadlose selfone en die rigting bepaal vir groter integrasie in die nabye toekoms.

Gevolgtrekking van hierdie referaat

Daar is nog steeds baie probleme met RF -integrasie. Elke RF -toestel van ‘n moderne selfoon word gekenmerk deur streng prestasievereistes. Die sensitiwiteitsvereiste is ongeveer – 106dbm (106db onder 1 MW) of hoër, en die ooreenstemmende vlak is slegs ‘n paar mikrovolt; Boonop behoort selektiwiteit, dit wil sê die verwerpingsvermoë van die bruikbare kanaal na die aangrensende frekwensieband (algemeen as blokkering genoem), in die orde van 60dB te wees; Daarbenewens moet die stelsel ossillator onder baie lae fase geraas werk om te voorkom dat voublokkerende energie die ontvangende band binnedring. RF -integrasie is baie moeilik vanweë die baie hoë frekwensie en uiters veeleisende prestasievereistes.

Die verwerking van multifrekwensie -standaard bring ‘n ware uitdaging vir die hele SOC -frekwensie. Daar word gehoop dat die opgewondenheid wat deur bandsending -oordrag veroorsaak word, verminder word. Die inhoud van digitale RF -integrasie is veel meer as om meer RF -komponente in een chip te plaas. ‘N Nuwe argitektuur vir die deel van hardeware is nodig.

Vir stelselontwerpers kan die huidige eenvoudige, hoogs geïntegreerde en koste-effektiewe halfgeleier-toestelle die ontwerpkompleksiteit aansienlik verminder. Terselfdertyd kan hulle die eienskappe van draadlose toestelle verryk en die stelselgrootte, batterylewe en koste onveranderd hou. Die nuwe hoogs geïntegreerde RF -toestelle kan ook ‘n paar geskille oor draadlose ontwerp uitskakel en ingenieurs se waardevolle tyd bespaar.