- 06

- Oct

ワイヤレスRF統合により、コンポーネントの数を減らし、回路基板の面積を減らします

コンポーネントの数を減らし、の面積を減らします 回路基板 ワイヤレスRF統合を介して

今日のワイヤレスデバイスでは、回路基板上のコンポーネントの半分以上がアナログRFデバイスです。 したがって、回路基板の面積と消費電力を削減する効果的な方法は、より大規模なRF統合を実行し、システムレベルのチップに向けて開発することです。 本稿では、RF統合の開発状況を紹介し、これらの問題のいくつかに対するいくつかの対策と解決策を提示します。

数年前、携帯電話市場はシングルバンドとデュアルバンドのシングルモード電話によって支配されていました、そして使用された技術はただでしたか? 全部でXNUMXつまたはXNUMXつのセルラーバンドを保持しますか? 同じ変調方式、マルチチャネルアクセス方式およびプロトコルが保持周波数帯域で採用されています。 対照的に、今日の新世代の携帯電話の設計ははるかに複雑で、マルチバンドとマルチモードを提供できますか? Bluetoothパーソナルエリアネットワーク、GPS測位などの機能を備えており、UWBやTV受信機能が登場し始めています。 さらに、ゲーム、画像、オーディオ、ビデオなどのアプリケーションが携帯電話で非常に一般的になっています。

ワイヤレス電話は、ハンドヘルドパーソナルエンターテインメントセンターと呼ばれる複雑なデバイスになりつつあります。 その開発傾向は、設計者により多くの課題をもたらし続けています。 新世代の携帯電話は、音声機能のみの携帯電話と比較して、通信処理、アプリケーション処理、RFインターフェースの数、統合メモリ容量が大幅に増加していますが、ユーザーは依然として携帯電話の音量が小さく、形状が合理化され、低いことを期待しています。価格と大型カラーディスプレイにより、従来の音声電話と同様の待機時間と通話時間を提供できます。 既存の全体的なサイズと消費電力を維持しながら、機能を指数関数的に増加させ、システム全体のコストを変更せずに維持することは、システム設計者に多くの問題を引き起こします。

明らかに、問題はシステム設計全体のすべての部分と、すべてのワイヤレス通信およびエンターテインメントコンテンツのサプライヤに関係しています。 ボード面積と消費電力の削減に特に効果的な領域の30つは、ワイヤレスシステム設計のRF部分です。 これは、今日の一般的な携帯電話では、ボード上のコンポーネントの半分以上がアナログRFコンポーネントであり、GPSやWLANなどのBluetooth RFシステムなどのボード領域全体の40〜XNUMX%を占めるためです。スペースの要件を増やします。

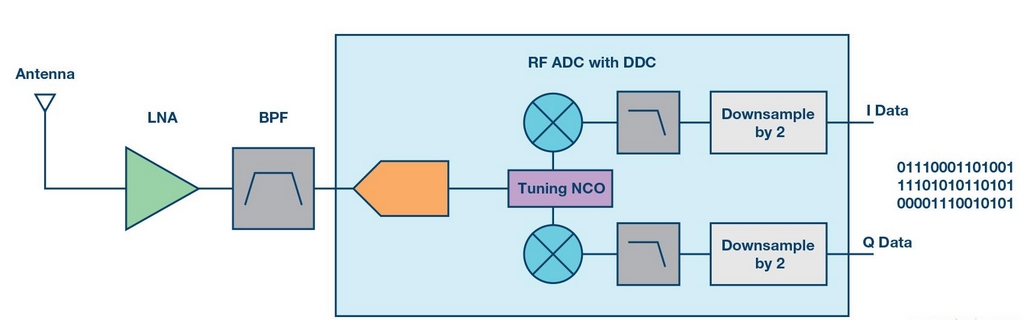

解決策は、より大規模なRF統合を実行し、最終的に完全に統合されたシステムレベルのチップに発展させることです。 一部の設計者は、RF機能に必要な回路基板の総スペースを削減するために、アナログ-デジタルコンバータをアンテナに配置しています。 半導体統合技術がより多くの機能を単一のデバイスに統合できる場合、ディスクリートデバイスの数とこれらのデバイスを収容するために使用される回路基板スペースはそれに応じて削減されます。 業界がシステムレベルのチップ統合に移行するにつれて、設計者は、小型ワイヤレスデバイスのRFの複雑さの増大とバッテリ寿命の延長との間の矛盾に対応するための新しいテクノロジを引き続き見つけていきます。

RF統合の開発状況

RF統合の重要な開発は、約1990年前に登場しました。 当時、RF技術とデジタルベースバンドモデムの開発により、スーパーヘテロダインRFデバイスをワイヤレス携帯電話の直接ダウンコンバージョン受信機に置き換えることが可能になりました。 スーパーヘテロダインRFデバイスは、多段ミキサー、フィルター、および長年使用されてきた複数の電圧制御発振器(VCO)を使用しますが、直接周波数変換RFデバイスを統合すると、GSMRFコンポーネントの総数を大幅に減らすことができます。 200年代後半、典型的なシングルバンドスーパーヘテロダインRFサブシステムには、PA、アンテナスイッチ、LDO、小信号RF、およびvctcxoが含まれ、約50の個別のデバイスが必要でした。 現在、VCO、VCXO、PLLループフィルターを統合した1バンド機能の直接周波数変換システムを設計できますが、コンポーネント数はXNUMX未満です。図XNUMX:高統合のXNUMXバンドGSMトランシーバー。

たとえば、Texas Instruments for GSMのトランシーバーtrf6151(図1)には、オンチップ電圧レギュレーター、VCOおよびVCOチャネル、PA電力制御、PLLループフィルターエッジブロッカー検出、LNAゲインステップバイステップ制御、およびVCXOが含まれています。

設計者にとって、高度な統合は、ワイヤレスRFのいくつかの主要な問題を克服するのに役立ちます。その中で最も基本的な問題は、DC電源とトランシーバーの調整です。 通話中は、温度や時間の変化に応じて電池電圧が変化します。 さらに、TXVCOおよびRxVCO電源からのノイズ結合もシステム全体のパフォーマンスに影響を与えます。 したがって、設計者は、RF回路基板レギュレータおよびほとんどの関連する受動部品をどのように解決するかという問題に直面しています。 これらのデバイスをRFトランシーバーに統合することは、必要な外部コンポーネントが電源に直接接続されている単純なデカップリングコンデンサだけであることを意味します。これにより、設計が簡素化されるだけでなく、回路基板のスペースも節約されます。

RF設計者にとってのもうXNUMXつの課題は、VCOのチューニング範囲とロック時間です。 すべてのアナログVCO設計。 多くの場合、ロック時間とチューニング範囲のバランスをとる必要があるため、ループフィルタは通常チップの外側に配置されます。 場合によっては、これはVCOチューニング範囲のソフトウェア制御で解決できます。 ただし、この方法では、電話の全体的な開発に追加のリソース要件が提示されます。 デジタルチューニング機能がVCOに含まれ、セルフキャリブレーションを提供できる場合、拡張されたチューニング範囲が得られ、ループフィルターエレメントをチップに配置できます。 明らかに、このスキームにより、設計エンジニアは作業を簡素化できます。

GSMシステムに必要な送信機の電力制御を取得するために、PAメーカーは通常、この機能をパワーアンプモジュール(PAM)に組み込んでいます。 パワーコントローラは通常、PAMの独立したチップで作成された最大数千のデジタルCMOSゲートで構成されています。 この要素により、PAMのコストが0.30〜0.40米ドル増加します。 この機能をRFデバイスに統合することで、GaAsPAMメーカーはデジタルCMOS回路を購入してPAMにインストールする必要がなくなります。 毎月数千の製品を製造しているOEMの場合、この冗長なコンポーネントを削除すると、コストが大幅に削減されます。

高度な統合によって大幅な節約が可能になるもう6151つの分野は、VCXOです。 以前は、高価なvctcxoモジュールが購入され、ディスクリートコンポーネントとしてRFデバイスで設計されていました。 したがって、vctcxoモジュールの一般的なコンポーネントをRFデバイスに組み込むことで、コストと関連する設計上の問題を減らすことができます。 trfXNUMXを使用すると、vctcxoの機能を完了するために必要なのは、低コストのクリスタルとバラクターのみです。

これらの統合と設計の簡素化にもかかわらず、RF設計エンジニアは依然として難しい選択に直面しています。そのXNUMXつは、入力感度とRx消費電力です。 低ノイズアンプ(LNA)の設計に使用される電流が大きいほど、全体的なノイズ特性が低くなることはよく知られています。 設計エンジニアは、受信機の総電力バジェットと受信機の感度レベル要件を決定する必要があります。 ただし、電力を減らしてもノイズは減少しません。 実際、それは反対です。 したがって、GSM規格の仕様を満たすことはできますが、設計者は、特定の感度レベルを達成するために消費電力の代償を払う価値があるかどうかを自問する必要があります。 この質問は、設計エンジニアとICメーカーが設計プロセス全体で緊密に協力する必要がある理由も説明しています。 設計エンジニアからのフィードバックは、将来のRF製品を開発する際に、ワイヤレス業界により良いサービスを提供するようにICメーカーを導くことができます。

SOCに向けた開発

ワイヤレスシステムのコスト、電力、および複雑さを削減することは、システム統合の要件を正常に満たすために非常に重要です。 しかし、携帯電話向けの高度な統合ソリューションの開発には、半導体業界が複雑な技術的障害を克服する必要があります。 これらの障害のいくつかは、必要なパフォーマンスを提供できる限り、SOCデバイスがどのように製造されているかを知りたくないため、設計者が気にすることはめったにありません。 したがって、携帯電話の統合に使用されるデバイスの機能と可用性に影響を与えるいくつかのプロセス技術をすばやく理解する必要があります。

携帯電話のRF電子システムを統合するためのいくつかの実行可能なスキームがあります。 まず、従来のRFアーキテクチャは、従来のテクノロジを使用して、比較的単純なバイポーラまたはBiCMOSプロセスで実装できます。 最終的なRFチップは、マルチチップパッケージングテクノロジ(システムレベルのパッケージングテクノロジ)を使用して、携帯電話のデジタルロジック機能と組み合わせることができます。 この技術には、使い慣れたRF設計手法や成熟したプロセスや技術を使用するなど、多くの利点がありますが、テストデバイスのコストと歩留まりが高いため、商業化は困難です。

さらに、携帯電話の電子システムの統合は、高度なBiCMOS(SiGe)ウェーハプロセスによっても実現できます。 ただし、SiGe HBTデバイスの処理には追加のリソグラフィプロセスが必要なため、最終的なチップには追加のコストが必要になります。 同時に、SiGe BiCMOSテクノロジは最先端のリソグラフィプロセスを使用できないため、BiCMOSプロセスは通常、高度なデジタルCMOSプロセスよりも遅れています。 これらは、携帯電話の特性を高め、コストを削減するという大きなプレッシャーをもたらします。 この技術ではシステムロジックやデジタル部品を常に可能な限り低い価格に保つことができないため、単純なウェーハプロセス戦略では解決できません。 したがって、BiCMOS(またはSiGe)にシステムベースバンド機能RF部分をモノリシックに統合することは適切な選択ではありません。

検討できる最終的な解決策は、CMOSへのRF統合であり、これもかなりの課題に直面しています。 いくつかのCMOSセルラーRF設計がありますが、これらの設計は主にアナログ機能に基づいています。 CMOSテクノロジを使用してアナログミキサー、フィルタ、および増幅器を実装することは困難であり、消費電力は一般にSiGeBiCMOSスキームよりも大きくなります。 プロセス技術の発展に伴い、CMOS定格レベルはますます低くなり、アナログ設計がより困難になっています。 新しいプロセスを開発する初期段階では、デバイスのモデリングとプロセスの成熟度は、一般に、アナログモジュールの設計に必要な高精度のパラメータモデリングの要件を満たすことができません。 ただし、最近開発されたデジタルCMOS RFアーキテクチャにより、モノリシックCMOS統合がより魅力的になります。

これらのソリューションは、メーカーが低コストのRFシステムレベルのチップソリューションを求めているため、半導体業界も牽引しています。 各統合スキームには困難がありますが、RFコンポーネントの統合がこれほど高いレベルに達する可能性があることは確かに驚くべきことです。 これらの困難を克服することは、無線携帯電話の設計において大きな一歩を踏み出し、近い将来、より大きな統合への方向性を設定するでしょう。

この論文の結論

RF統合にはまだ多くの困難があります。 最新の携帯電話のすべてのRFデバイスは、厳しいパフォーマンス要件に直面しています。 感度要件は約– 106dbm(106 MW未満の1db)以上であり、対応するレベルはわずか数マイクロボルトです。 さらに、選択性、つまり、隣接する周波数帯域に対する有用なチャネルの除去能力(一般にブロッキングと呼ばれる)は、60dBのオーダーである必要があります。 さらに、システム発振器は、フォールディングブロッキングエネルギーが受信帯域に入るのを防ぐために、非常に低い位相ノイズの下で動作する必要があります。 非常に高い周波数と非常に厳しいパフォーマンス要件のため、RF統合は非常に困難です。

マルチ周波数規格の処理は、SOC周波数全体に真の課題をもたらします。 帯域内信号伝送によって生成される励起を低減することが望まれます。 デジタルRF統合の内容は、複数のRFコンポーネントをXNUMXつのチップに配置するだけではありません。 ハードウェア共有の新しいアーキテクチャが必要です。

システム設計者にとって、現在のシンプルで高度に統合された費用効果の高い半導体デバイスは、設計の複雑さを大幅に軽減することができます。 同時に、ワイヤレスデバイスの特性を強化し、システムサイズ、バッテリー寿命、およびコストを変更せずに維持できます。 新しい高度に統合されたRFデバイスは、ワイヤレス設計におけるいくつかの論争を排除し、エンジニアの貴重な時間を節約することもできます。