- 06

- Oct

Reduzéiert d’Zuel vun de Komponenten a reduzéiert d’Gebitt vum Circuit Board duerch drahtlose RF Integratioun

Reduzéiert d’Zuel vun de Komponenten a reduzéiert d’Gebitt vun Circuit Verwaltungsrot duerch drahtlose RF Integratioun

An de haitegen drahtlosen Apparater si méi wéi d’Halschent vun de Komponenten um Circuit Board analog RF Geräter. Dofir ass en effektive Wee fir de Circuit Board Beräich a Stroumverbrauch ze reduzéieren méi grouss Skala RF Integratioun auszeféieren an Richtung Systemniveau Chip z’entwéckelen. Dëse Pabeier féiert den Entwécklungsstatus vun der RF Integratioun vir, a stellt e puer Géigner a Léisunge fir e puer vun dëse Probleemer vir.

Virun e puer Joer war den Handy Maart vun Single Band an Dual Band Single-Mode Handyen dominéiert, an d’Technologie benotzt war nëmmen ??? Halt een oder zwee Cellular Bands am ganzen ??? Déi selwecht Modulatiounsmethod, Multi-Kanal Zouganksschema a Protokoll ginn an der Haltfrequenzband ugeholl. Am Géigesaz, den Design vun der neier Generatioun vun haut ass méi komplex a ka Multi Band a Multi-Modus ubidden ??? Et huet Bluetooth perséinlecht Gebittsnetzwierk, GPS Positionéierung an aner Funktiounen, an UWB an Fernsehempfänger hunn ugefaang ze erschéngen. Zousätzlech sinn Uwendungen wéi Spiller, Biller, Audio a Video ganz heefeg ginn an Handyen.

Wireless Telefon gëtt zu engem komplexe Apparat mam Handheld Personal Entertainment Center. Säin Entwécklungstrend bréngt weider Designer Erausfuerderunge mat sech. Och wann am Verglach mat Handyen mat nëmmen Stëmmfunktioun, déi nei Generatioun vun Handyen wesentlech eropgaang ass a Kommunikatiounsveraarbechtung, Uwendungsveraarbechtung, d’Zuel vu RF Interfaces an integréiert Erënnerungskapazitéit, erwaarden d’Benotzer ëmmer nach datt Handyen e méi klenge Volumen hunn, streamlined Form, niddereg Präis a grousse Faarfdisplay, Et kann Standby a Gespréichszäit ubidden ähnlech wéi traditionell Stëmm Handyen. Déi existéierend Gesamtgréisst a Stroumverbrauch behalen, awer d’Funktioun exponentiell erhéijen, wärend d’Gesamtkäschte onverännert bleiwen, stellen all dës vill Probleemer fir d’Systemdesigner.

Natierlech enthält de Problem all Deeler vum ganzen Systemdesign, souwéi d’Liwweranten vun all drahtlose Kommunikatioun an Ënnerhalungsinhalt. Ee Beräich dat besonnesch effektiv ass fir d’Bordfläch an den Energieverbrauch ze reduzéieren ass de RF Deel vum Wireless System Design. Dëst ass well am haitegen typeschen Handy méi wéi d’Halschent vun de Komponente um Bord analog RF Komponenten sinn, déi zesummen 30-40% vum ganze Boardberäich ausmaachen, sou wéi Bluetooth RF Systemer wéi GPS a WLAN wäerten och immens Erhéijung vun den Ufuerderunge fir de Raum.

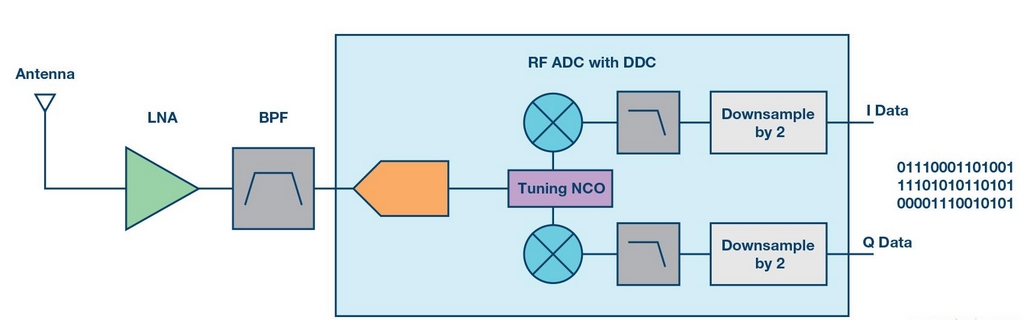

D’Léisung ass méi grouss RF-Integratioun auszeféieren an endlech zu engem voll integréierten Systemniveau Chip z’entwéckelen. E puer Designer hunn Analog-zu-Digital Konverter an d’Antenne gesat fir den Total Circuit Board Raum fir RF Funktiounen ze reduzéieren. Wann Hallefleitintegratiounstechnologie méi Funktiounen an engem eenzegen Apparat integréiere kann, gëtt d’Zuel vun diskreten Apparater an de Circuit Board Raum benotzt fir dës Apparater z’empfänken entspriechend reduzéiert. Wéi d’Industrie sech Richtung Systemniveau Chip Integratioun beweegt, wäerten Designer weider nei Technologien fannen fir de Widdersproch tëscht méi héijer RF Komplexitéit a méi laang Batterie lieweg a klenge Funkgeräter z’erreechen.

Entwécklungsstatus vun der RF Integratioun

Eng wichteg Entwécklung vun der RF Integratioun erschéngt virun ongeféier zwee Joer. Zu där Zäit huet d’Entwécklung vu RF Technologie an digitale Baseband Modem et erméiglecht Superheterodyne RF Apparater duerch direkt Down Konversiounsempfänger op drahtlose Handyen ze ersetzen. Superheterodyne RF Apparater benotze Multistage Mixer, Filteren a Multiple Spannungskontrolléiert Oszillatoren (VCOs), déi fir vill Jore gutt benotzt goufen, awer d’Integratioun vun direkten Frequenz Konversioun RF Apparater kënnen d’Gesamtzuel vun GSM RF Komponenten immens reduzéieren. Um Enn vun den 1990er Joren enthält en typesche Single Band Superheterodyne RF Subsystem PA, Antenneschalter, LDO, klengt Signal RF a vctcxo, erfuerdert ongeféier 200 diskret Geräter; Haut kënne mir en direkten Frequenz Konversiounssystem mat véier Band Funktioun designen, déi VCO, VCXO a PLL Loop Filter integréiert, awer seng Unzuel vun Komponenten ass manner wéi 50. Figur 1: Véier Band GSM Sender / Empfänger mat héijer Integratioun.

Zum Beispill enthält den Transceiver trf6151 (Figure 1) vun Texas Instruments fir GSM On-Chip Spannungsregulator, VCO a VCO Kanal, PA Stroumkontroll, PLL Loop Filter Rand Blocker Detektioun, LNA Gewënn Schrëtt fir Schrëtt Kontroll a VCXO.

Fir Designer hëlleft fortgeschratt Integratioun e puer gréisser Probleemer am drahtlose RF ze iwwerwannen, ënner deenen déi meescht Basis ass d’DC Stroumversuergung a Reguléierung vum Sender / Empfänger. Wärend engem Uruff ännert d’Batteriespannung mat der Ännerung vun Temperatur an Zäit. Zousätzlech wäert d’Rauschkupplung vun TX VCO a Rx VCO Energieversuergung och d’Leeschtung vum ganze System beaflossen. Dofir sti Designer mam Problem konfrontéiert wéi de RF Circuit Board Regulator a meescht verbonne passiv Komponenten ze léisen. Dës Apparater an den RF Sender ze integréieren heescht datt déi eenzeg extern Komponent erfuerderlech ass en einfachen Ofkupplungskondensator, deen direkt mat der Energieversuergung ugeschloss ass, wat net nëmmen den Design vereinfacht, awer och de Circuit Board Raum spuert.

Eng aner Erausfuerderung fir RF Designer ass VCO Tuning Range a Sperrzäit. An all analoge VCO Designs. Well et dacks noutwendeg ass d’Sperrzäit an d’Tuningbereich ze balanséieren, gëtt de Loopfilter normalerweis ausserhalb vum Chip gesat. Heiansdo kann dëst an der Software Kontroll vu VCO Tuning Range geléist ginn. Wéi och ëmmer, dës Method stellt zousätzlech Ressource Ufuerderunge fir d’Gesamtentwécklung vum Telefon vir. Wann déi digital Tuning Funktioun am VCO abegraff ass a Selbstkalibratioun ka liwweren, kann en erweiderten Tuningbereich kritt ginn, an d’Loopfilterelement kann am Chip gesat ginn. Natierlech kann dëse Schema Designingenieuren et erméiglechen hir Aarbecht ze vereinfachen.

Fir d’Sender Muecht Kontroll ze kréien, déi vum GSM System erfuerderlech ass, enthalen PA Hiersteller allgemeng dës Funktioun am Kraaftverstärker Modul (PAM). De Power Controller besteet normalerweis aus bis zu Dausende vun digitale CMOS Tore, déi an engem onofhängege Chip am PAM gemaach ginn. Dëst Element wäert d’Käschte vum PAM ëm US $ 0.30 ~ 0.40 erhéijen. Dës Funktioun an RF Geräter z’integréieren erlaabt GaAs PAM Hiersteller keng digital CMOS Kreesser ze kafen an se an PAM z’installéieren. Fir en OEM, deen all Mount Dausende vu Produkter produzéiert, wäert dës redundante Komponent ewechhuelen hir Käschte staark reduzéieren.

En anert Gebitt wou fortgeschratt Integratioun substantiell Spuer brénge kann ass VCXO. An der Vergaangenheet goufen deier vctcxo Moduler kaaft an entworf a RF Geräter als diskret Komponenten. Dofir kann d’komponent Komponente vu vctcxo Moduler an RF Geräter integréieren d’Käschte reduzéieren a verbonne Designprobleemer. Benotzt trf6151 sinn nëmmen e bëllege Kristall a Varaktor noutwendeg fir d’Funktioun vu vctcxo ze kompletéieren.

Trotz dëser Integratioun an Design Vereinfachung, stellen RF Designingenieuren ëmmer nach schwiereg Wiel, eng vun deenen ass Input Empfindlechkeet a Rx Stroumverbrauch. Et ass bekannt datt wat méi grouss de Stroum am Design vum nidderegen Geräischer Verstärker (LNA) benotzt gëtt, wat déi allgemeng Kaméidi Charakteristike méi niddereg sinn. Den Designingenieur muss de Gesamtkraaftbudget vum Empfänger an d’Sensibilitéitsniveau Ufuerderunge vum Empfänger bestëmmen. Wéi och ëmmer, de Kaméidi geet net erof mat der Reduktioun vun der Muecht. Tatsächlech ass et de Géigendeel. Dofir, och wann et den GSM Standard Spezifikatioun entsprécht, mussen Designer sech dacks froen ob et derwäert ass de Präis am Stroumverbrauch ze bezuelen fir e gewësse Empfindlechkeetniveau z’erreechen. Dës Fro erkläert och firwat et noutwendeg ass fir Designingenieuren an IC Hiersteller eng enk Zesummenaarbecht am ganzen Designprozess ze hunn. De Feedback vun Designingenieuren kënne IC Hiersteller guidéieren fir déi drahtlos Industrie besser ze déngen wann se zukünfteg RF Produkter entwéckelen.

Entwéckelt a Richtung SOC

D’Käschte reduzéieren, Kraaft a Komplexitéit vu Funk Systemer ass ganz wichteg fir erfollegräich den Ufuerderunge vun der Systemintegratioun gerecht ze ginn. Wéi och ëmmer, d’Entwécklung vun héich Integratiounsléisunge fir Handyen erfuerdert d’Hallefleitindustrie fir komplex technesch Hindernisser ze iwwerwannen. E puer vun dësen Hindernisser si selten vun Designer besuergt, well vill vun hinnen wëllen net wëssen wéi SOC Apparater hiergestallt ginn, Soulaang et déi erfuerderlech Leeschtung ka liwweren. Dofir ass et noutwendeg e séiere Verständnis vun e puer Prozestechnologien ze hunn, wat d’Kapazitéit an d’Disponibilitéit vun Apparater beaflosst, déi an der Handyintegratioun benotzt ginn.

Et gi verschidde machbar Schemae fir d’Integratioun vum Handy RF elektronesche System. Als éischt kann eng traditionell RF Architektur an engem relativ einfache bipolare oder BiCMOS Prozess implementéiert ginn mat traditioneller Technologie. Dee leschte RF Chip ka mat Handy digitaler Logikfunktiounen zesummegesat ginn mat Multi Chip Verpackungstechnologie (Systemniveau Verpackungstechnologie). Och wann dës Technologie vill Virdeeler huet, sou wéi d’Benotzung vu bekannte RF Designmethoden a reife Prozesser an Technologien, ass et schwéier ze kommerzialiséieren wéinst den héije Käschte an Ausbezuele vun Testapparater.

Zousätzlech kann d’Integratioun vum Handy elektronesche System och duerch fortgeschratt BiCMOS (SiGe) Waferprozess kritt ginn. Wéi och ëmmer, well d’Veraarbechtung vu SiGe HBT Apparater en zousätzleche Lithographieprozess erfuerdert, erfuerdert de leschte Chip zousätzlech Käschten. Zur selwechter Zäit, well SiGe BiCMOS Technologie den fortgeschrattste Lithographieprozess net ka benotzen, bleift de BiCMOS Prozess normalerweis hannert dem fortgeschrattem digitale CMOS Prozess. Dës bréngen e groussen Drock fir d’Charakteristike vun Handyen ze erhéijen an d’Käschten ze reduzéieren. Et kann net mat enger einfacher Waferprozessstrategie geléist ginn, well dës Technologie kann d’Systemlogik oder den digitalen Deel zu allen Zäiten um niddregsten Präis net halen. Dofir ass monolithesch Integratioun vum System Baseband Funktioun RF Deel a BiCMOS (oder SiGe) keng gutt Wiel.

Déi lescht Léisung déi berécksiichtegt ka ginn ass RF Integratioun a CMOS, déi och bedeitend Erausfuerderunge stellen. Och wann et verschidde CMOS cellulär RF Designer sinn, sinn dës Designs gréisstendeels baséiert op analoge Funktiounen. Et ass schwéier analog Analogmixer, Filteren an Verstärker mat CMOS Technologie z’implementéieren, an den Energieverbrauch ass allgemeng méi grouss wéi SiGe BiCMOS Schema. Mat der Entwécklung vu Prozestechnologie gëtt den CMOS bewäerten Niveau ëmmer méi niddereg, wat den analoge Design méi schwéier mécht. Am fréie Stadium vun der Entwécklung vun neie Prozesser kënnen Apparatmodellerung a Prozessmaturitéit allgemeng net den Ufuerderunge vun héichpräzis Parametermodellerung erfëllen fir den Analog Modul Design. Wéi och ëmmer, déi kierzlech entwéckelt digital CMOS RF Architektur mécht d’monolithesch CMOS Integratioun méi attraktiv.

Dës Léisunge féieren och d’Hallefleitindustrie wéi d’Fabrikanten no bëlleg RF Systemniveau Chipléisungen sichen. Och wann all Integratiounsschema Schwieregkeeten huet, ass et wierklech iwwerraschend datt RF Komponent Integratioun sou en héijen Niveau kann erreechen. Dës Schwieregkeeten ze iwwerwannen hëlt e grousse Schrëtt no vir am Design vu drahtlosen Handyen a setzt d’Richtung fir eng gréisser Integratioun an der nächster Zukunft.

Conclusioun vun dësem Pabeier

Et gi nach ëmmer vill Schwieregkeeten an der RF Integratioun. All RF -Apparat vum modernen Handy steet mat strenge Leeschtungsufuerderungen. D’Sensibilitéitsfuerderung ass ongeféier – 106dbm (106db ënner 1 MW) oder méi héich, an den entspriechenden Niveau ass nëmmen e puer Mikrovolt; Zousätzlech soll d’Selektivitéit, dat heescht d’Oflehnungsfäegkeet vum nëtzlechen Kanal zum benachbarte Frequenzband (allgemeng als Blockéierung bezeechent), an der Uerdnung vun 60dB sinn; Zousätzlech ass de System Oszilléierer erfuerdert ënner ganz nidderegen Phas Geräischer ze bedreiwen fir ze vermeiden datt klappt blockéierend Energie an den Empfangsband erakënnt. RF Integratioun ass ganz schwéier wéinst der ganz héijer Frequenz an extrem usprochsvollen Performance Ufuerderunge.

D’Veraarbechtung vu Multi Frequenz Standard bréngt eng reell Erausfuerderung fir déi ganz SOC Frequenz. Et gëtt gehofft d’Excitatioun ze reduzéieren, generéiert duerch Bandsignal Iwwerdroung. Den Inhalt vun der digitaler RF Integratioun ass vill méi wéi verschidde RF Komponenten an engem Chip ze setzen. Eng nei Architektur fir Hardware Sharing ass gebraucht.

Fir Systemdesigner kënnen déi aktuell einfach, héich integréiert a kosteneffektiv Hallefleitgeräter d’Design Komplexitéit staark reduzéieren. Zur selwechter Zäit kënne se d’Charakteristike vu drahtlosen Apparater beräicheren an d’Systemgréisst, d’Batteriedauer an d’Käschte onverännert behalen. Déi nei héich integréiert RF Geräter kënnen och e puer Streidereien am drahtlose Design eliminéieren an wäertvoll Zäit vun Ingenieuren spueren.