- 06

- Oct

Reduza o número de componentes e reduza a área da placa de circuito por meio da integração de RF sem fio

Reduza o número de componentes e reduza a área de placa de circuito por meio da integração de RF sem fio

Nos dispositivos sem fio de hoje, mais da metade dos componentes da placa de circuito são dispositivos RF analógicos. Portanto, uma maneira eficaz de reduzir a área da placa de circuito e o consumo de energia é realizar uma integração de RF em maior escala e desenvolver um chip de nível de sistema. Este documento apresenta o status de desenvolvimento da integração de RF e apresenta algumas contramedidas e soluções para alguns desses problemas.

Há alguns anos, o mercado de telefonia celular era dominado por telefones single band e dual band single-mode, e a tecnologia usada era apenas ??? Segure uma ou duas bandas de celular ao todo ??? O mesmo método de modulação, esquema de acesso multicanal e protocolo são adotados na banda de frequência de manutenção. Em contraste, o design da nova geração de telefones celulares de hoje é muito mais complexo e pode fornecer multibanda e multimodo ??? Possui rede de área pessoal Bluetooth, posicionamento GPS e outras funções, e as funções de recepção de UWB e TV começaram a aparecer. Além disso, aplicativos como jogos, imagens, áudio e vídeo se tornaram muito comuns em telefones celulares.

O telefone sem fio está se tornando um dispositivo complexo chamado centro de entretenimento pessoal portátil. Sua tendência de desenvolvimento continua a trazer mais desafios aos designers. Embora em comparação com telefones celulares com apenas função de voz, a nova geração de telefones celulares aumentou significativamente no processamento de comunicação, processamento de aplicativos, o número de interfaces RF e capacidade de memória integrada, os usuários ainda esperam que os telefones celulares tenham um volume menor, formato simplificado, baixo preço e grande display colorido, pode fornecer tempo de espera e conversação semelhante aos telefones de voz tradicionais. Manter o tamanho geral e o consumo de energia existentes, mas fazer a função aumentar exponencialmente, enquanto mantém o custo geral do sistema inalterado, tudo isso representa muitos problemas para os projetistas do sistema.

Obviamente, o problema envolve todas as partes de todo o projeto do sistema, bem como os fornecedores de todo o conteúdo de comunicação e entretenimento sem fio. Uma área que é particularmente eficaz na redução da área da placa e do consumo de energia é a parte RF do projeto do sistema sem fio. Isso ocorre porque no telefone móvel típico de hoje, mais da metade dos componentes na placa são componentes RF analógicos, que juntos respondem por 30-40% de toda a área da placa, como sistemas Bluetooth RF, como GPS e WLAN, também são muito aumentar os requisitos de espaço.

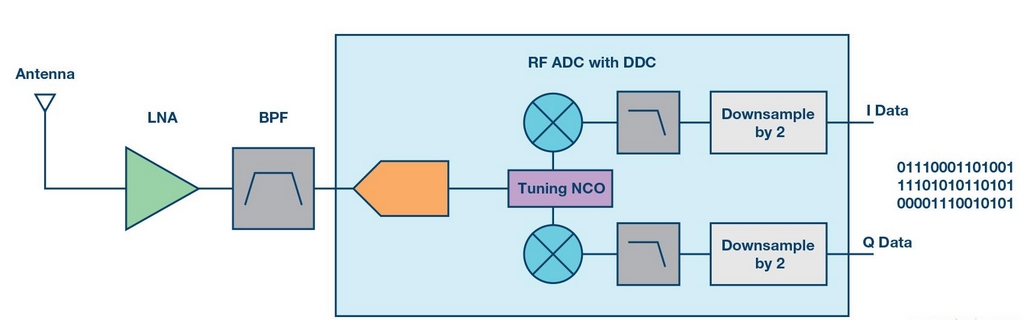

A solução é realizar mais integração de RF em grande escala e, finalmente, desenvolver um chip de nível de sistema totalmente integrado. Alguns projetistas colocam conversores analógico-digital na antena para reduzir o espaço total da placa de circuito necessário para funções de RF. Quando a tecnologia de integração de semicondutores pode integrar mais funções em um único dispositivo, o número de dispositivos discretos e o espaço da placa de circuito usado para acomodar esses dispositivos serão reduzidos de acordo. À medida que a indústria avança em direção à integração de chips em nível de sistema, os projetistas continuarão a encontrar novas tecnologias para atender à contradição entre maior complexidade de RF e maior vida útil da bateria em pequenos dispositivos sem fio.

Status de desenvolvimento da integração RF

Um importante desenvolvimento da integração de RF apareceu há cerca de dois anos. Naquela época, o desenvolvimento da tecnologia RF e do modem de banda base digital tornou possível substituir os dispositivos RF super-heteródinos por receptores de conversão direta em telefones móveis sem fio. Dispositivos de RF super-heteródinos usam misturadores de vários estágios, filtros e osciladores controlados por tensão múltipla (VCOs), que têm sido bem usados por muitos anos, mas a integração de dispositivos de RF de conversão de frequência direta pode reduzir muito o número total de componentes de RF GSM. No final da década de 1990, um subsistema de RF super-heteródino de banda única típico incluía PA, switch de antena, LDO, RF de pequeno sinal e vctcxo, exigindo cerca de 200 dispositivos discretos; Hoje, podemos projetar um sistema de conversão direta de frequência com função de quatro bandas, que integra VCO, VCXO e filtro de loop PLL, mas seu número de componentes é inferior a 50. Figura 1: Transceptor GSM de quatro bandas com alta integração.

Por exemplo, o transceptor trf6151 (Figura 1) da Texas Instruments para GSM inclui regulador de tensão no chip, canal VCO e VCO, controle de potência PA, detecção de bloqueio de borda de filtro de loop PLL, controle passo a passo de ganho LNA e VCXO.

Para os projetistas, a integração avançada ajuda a superar alguns dos principais problemas de RF sem fio, entre os quais o mais básico é a fonte de alimentação CC e a regulação do transceptor. Durante uma chamada, a voltagem da bateria mudará com a mudança de temperatura e tempo. Além disso, o acoplamento de ruído da fonte de alimentação TX VCO e Rx VCO também afetará o desempenho de todo o sistema. Portanto, os projetistas se deparam com o problema de como resolver o regulador da placa de circuito de RF e a maioria dos componentes passivos relacionados. Integrar esses dispositivos ao transceptor de RF significa que o único componente externo necessário é um capacitor de desacoplamento simples, que é conectado diretamente à fonte de alimentação, o que não apenas simplifica o design, mas também economiza espaço na placa de circuito.

Outro desafio para os projetistas de RF é o intervalo de sintonia VCO e o tempo de bloqueio. Em todos os projetos VCO analógicos. Como geralmente é necessário equilibrar o tempo de travamento e a faixa de sintonia, o filtro de loop geralmente é colocado fora do chip. Às vezes, isso pode ser resolvido no controle de software da faixa de sintonia VCO. No entanto, este método apresenta requisitos de recursos adicionais para o desenvolvimento geral do telefone. Quando a função de sintonia digital está incluída no VCO e pode fornecer autocalibração, uma faixa de sintonia estendida pode ser obtida e o elemento de filtro de loop pode ser colocado no chip. Obviamente, esse esquema pode permitir que os engenheiros de projeto simplifiquem seu trabalho.

Para obter o controle de potência do transmissor exigido pelo sistema GSM, os fabricantes de PA geralmente incluem essa função no módulo amplificador de potência (PAM). O controlador de energia normalmente é composto de até milhares de portas CMOS digitais, que são feitas em um chip independente no PAM. Este elemento aumentará o custo do PAM em US $ 0.30 ~ 0.40. A integração desta função em dispositivos RF permitirá que os fabricantes de PAM GaAs não comprem circuitos CMOS digitais e os instalem no PAM. Para um OEM que produz milhares de produtos todos os meses, a remoção desse componente redundante reduzirá muito seu custo.

Outra área onde a integração avançada pode trazer economias substanciais é o VCXO. No passado, módulos vctcxo caros eram adquiridos e projetados em dispositivos RF como componentes discretos. Portanto, a incorporação de componentes comuns de módulos vctcxo em dispositivos de RF pode reduzir custos e problemas de design relacionados. Usando trf6151, apenas um cristal e varactor de baixo custo são necessários para completar a função de vctcxo.

Apesar dessa integração e simplificação do projeto, os engenheiros de projeto de RF ainda enfrentam escolhas difíceis, uma das quais é a sensibilidade de entrada e o consumo de energia Rx. É bem conhecido que quanto maior a corrente usada no projeto do amplificador de baixo ruído (LNA), menores são as características gerais de ruído. O engenheiro de projeto deve determinar o orçamento total de energia do receptor e os requisitos de nível de sensibilidade do receptor. Porém, o ruído não diminui com a redução da potência. Na verdade, é o oposto. Portanto, embora possa atender à especificação do padrão GSM, os projetistas costumam se perguntar se vale a pena pagar o preço no consumo de energia para atingir um determinado nível de sensibilidade. Essa pergunta também explica por que é necessário que os engenheiros de projeto e os fabricantes de CI cooperem estreitamente em todo o processo de projeto. O feedback dos engenheiros de projeto pode orientar os fabricantes de IC para melhor servir a indústria sem fio ao desenvolver futuros produtos de RF.

Desenvolvendo para SOC

Reduzir o custo, a potência e a complexidade dos sistemas sem fio é muito importante para atender aos requisitos de integração do sistema com sucesso. No entanto, o desenvolvimento de soluções de alta integração para telefones celulares exige que a indústria de semicondutores supere obstáculos técnicos complexos. Alguns desses obstáculos raramente são preocupados pelos designers, porque muitos deles não querem saber como os dispositivos SOC são feitos, desde que possam fornecer o desempenho necessário. Portanto, é necessário ter um rápido entendimento de algumas tecnologias de processo, que afetarão a capacidade e a disponibilidade dos dispositivos usados na integração de telefones celulares.

Existem vários esquemas viáveis para a integração do sistema eletrônico de RF de telefone móvel. Em primeiro lugar, uma arquitetura de RF tradicional pode ser implementada em um processo bipolar ou BiCMOS relativamente simples usando tecnologia tradicional. O chip RF final pode ser montado com funções de lógica digital de telefone celular usando a tecnologia de empacotamento de vários chips (tecnologia de empacotamento de nível de sistema). Embora essa tecnologia tenha muitas vantagens, como o uso de métodos familiares de projeto de RF e processos e tecnologias maduros, é difícil de comercializar devido ao alto custo e rendimento dos dispositivos de teste.

Além disso, a integração do sistema eletrônico do telefone móvel também pode ser obtida pelo avançado processo de wafer BiCMOS (SiGe). No entanto, como o processamento de dispositivos SiGe HBT requer processo de litografia adicional, o chip final exigirá um custo adicional. Ao mesmo tempo, como a tecnologia SiGe BiCMOS não pode usar o processo de litografia mais avançado, o processo BiCMOS geralmente fica atrás do processo CMOS digital avançado. Isso trará grande pressão para aumentar as características dos telefones celulares e reduzir custos. Isso não pode ser resolvido com uma estratégia de processo de wafer simples, porque esta tecnologia não consegue manter a lógica do sistema ou a parte digital com o menor preço possível em todos os momentos. Portanto, a integração monolítica da parte de RF da banda base do sistema no BiCMOS (ou SiGe) não é uma boa escolha.

A solução final que pode ser considerada é a integração de RF em CMOS, que também enfrenta desafios consideráveis. Embora existam vários designs de RF celular CMOS, esses designs são amplamente baseados em funções analógicas. É difícil implementar mixers, filtros e amplificadores analógicos com tecnologia CMOS, e o consumo de energia é geralmente maior do que o esquema SiGe BiCMOS. Com o desenvolvimento da tecnologia de processo, o nível nominal do CMOS está ficando cada vez mais baixo, o que torna o projeto analógico mais difícil. No estágio inicial de desenvolvimento de novos processos, a modelagem de dispositivo e a maturidade do processo geralmente não podem atender aos requisitos de modelagem de parâmetros de alta precisão exigidos para o projeto de módulo analógico. No entanto, a arquitetura CMOS RF digital recentemente desenvolvida torna a integração CMOS monolítica mais atraente.

Essas soluções também impulsionam a indústria de semicondutores, à medida que os fabricantes buscam soluções de chip de nível de sistema de RF de baixo custo. Embora cada esquema de integração tenha dificuldades, é realmente surpreendente que a integração de componentes de RF possa atingir um nível tão alto. Superar essas dificuldades representará um grande passo em frente no design de telefones celulares sem fio e definirá a direção para uma maior integração em um futuro próximo.

Conclusão deste artigo

Ainda existem muitas dificuldades na integração RF. Cada dispositivo RF de um telefone móvel moderno enfrenta rígidos requisitos de desempenho. O requisito de sensibilidade é de cerca de – 106dbm (106db abaixo de 1 MW) ou superior, e o nível correspondente é de apenas alguns microvolts; Além disso, a seletividade, ou seja, a capacidade de rejeição do canal útil para a faixa de frequência adjacente (comumente referida como bloqueio), deve ser da ordem de 60dB; Além disso, o oscilador do sistema deve operar sob ruído de fase muito baixo para evitar que a energia de bloqueio de dobra entre na banda de recepção. A integração de RF é muito difícil devido à frequência muito alta e aos requisitos de desempenho extremamente exigentes.

O padrão de processamento multifrequencial traz um verdadeiro desafio para toda a frequência SOC. Espera-se reduzir a excitação gerada pela transmissão do sinal em banda. O conteúdo da integração de RF digital é muito mais do que colocar vários componentes de RF em um único chip. Uma nova arquitetura de compartilhamento de hardware é necessária.

Para projetistas de sistemas, os atuais dispositivos semicondutores simples, altamente integrados e econômicos podem reduzir muito a complexidade do projeto. Ao mesmo tempo, eles podem enriquecer as características dos dispositivos sem fio e manter o tamanho do sistema, a vida útil da bateria e o custo inalterados. Os novos dispositivos RF altamente integrados também podem eliminar algumas disputas no design sem fio e economizar o valioso tempo dos engenheiros.