- 06

- Oct

通過無線射頻集成,減少元器件數量,減少電路板面積

減少元件數量,減少面積 電路板 通過無線射頻集成

在當今的無線設備中,電路板上一半以上的元件都是模擬射頻設備。 因此,減少電路板面積和功耗的有效途徑是進行更大規模的射頻集成,向系統級芯片發展。 本文介紹了射頻集成的發展現狀,並針對其中一些問題提出了一些對策和解決方案。

幾年前,手機市場以單頻和雙頻單模手機為主,所用的技術只有??? 總共持有一兩個蜂窩頻段??? 保持頻段採用相同的調製方式、多路接入方案和協議。 相比之下,今天新一代手機的設計要復雜得多,可以提供多頻段和多模??? 具有藍牙個域網、GPS定位等功能,UWB和電視接收功能也開始出現。 此外,遊戲、圖像、音頻和視頻等應用在手機中也變得非常普遍。

無線電話正在成為一種稱為手持個人娛樂中心的複雜設備。 它的發展趨勢不斷給設計師帶來更多的挑戰。 儘管與僅有語音功能的手機相比,新一代手機在通信處理、應用處理、射頻接口數量和集成內存容量等方面都有顯著提升,但用戶仍然期望手機具有更小的體積、流線型的外形、低價格實惠,彩色大顯示屏,可提供類似於傳統語音電話的待機和通話時間。 保持現有的整體尺寸和功耗,但使功能成倍增加,同時保持整體系統成本不變,這些都給系統設計人員帶來了很多問題。

顯然,問題涉及到整個系統設計的各個部分,以及所有無線通信和娛樂內容的供應商。 在減少電路板面積和功耗方面特別有效的一個領域是無線系統設計的 RF 部分。 這是因為在當今典型的手機中,板上一半以上的元件都是模擬射頻元件,它們加起來佔整個電路板面積的 30-40%,例如 GPS 和 WLAN 等藍牙射頻系統也將大大增加增加對空間的要求。

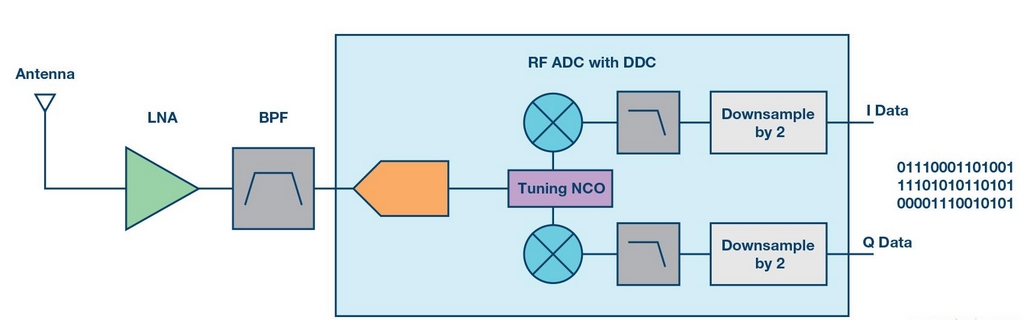

解決方案是進行更大規模的射頻集成,最終發展成全集成的系統級芯片。 一些設計人員將模數轉換器放入天線中,以減少射頻功能所需的總電路板空間。 當半導體集成技術可以在單個器件中集成更多功能時,分立器件的數量和用於容納這些器件的電路板空間將相應減少。 隨著行業朝著系統級芯片集成的方向發展,設計人員將不斷尋找新技術來解決小型無線設備中更高的 RF 複雜性和更長的電池壽命之間的矛盾。

射頻集成發展現狀

大約兩年前出現了射頻集成的重要發展。 當時,射頻技術和數字基帶調製解調器的發展使得在無線手機中用直接下變頻接收器代替超外差射頻器件成為可能。 超外差射頻器件使用多級混頻器、濾波器和多個壓控振盪器(VCO),這些已經很好地使用了多年,但是直接變頻射頻器件的集成可以大大減少 GSM 射頻組件的總數。 1990 年代後期,典型的單頻段超外差射頻子系統包括 PA、天線開關、LDO、小信號射頻和 vctcxo,需要大約 200 個分立器件; 今天,我們可以設計一個具有四頻段功能的直接變頻系統,它集成了VCO、VCXO和PLL環路濾波器,但其元件數量不到50個。圖1:高集成度的四頻段GSM收發器。

例如,德州儀器 (TI) 的 GSM 收發器 trf6151(圖 1)包括片上穩壓器、VCO 和 VCO 通道、PA 功率控制、PLL 環路濾波器邊緣阻塞檢測、LNA 增益步進控制和 VCXO。

對於設計人員來說,高級集成有助於克服無線射頻中的一些主要問題,其中最基本的問題是收發器的直流電源和調節。 在通話過程中,電池電壓會隨著溫度和時間的變化而變化。 此外,TX VCO 和 Rx VCO 電源的噪聲耦合也會影響整個系統的性能。 因此,設計人員面臨著如何解決射頻電路板穩壓器和大部分相關無源元件的問題。 將這些器件集成到射頻收發器中,意味著只需要一個簡單的去耦電容,直接連接到電源,不僅可以簡化設計,還可以節省電路板空間。

RF 設計人員面臨的另一個挑戰是 VCO 調諧範圍和鎖定時間。 在所有模擬 VCO 設計中。 因為經常需要平衡鎖定時間和調諧範圍,所以環路濾波器通常放置在芯片外部。 有時,這可以通過 VCO 調諧範圍的軟件控制來解決。 但是,這種方式對電話的整體發展提出了額外的資源需求。 當VCO中包含數字調諧功能並且可以提供自校準時,可以獲得擴展的調諧範圍,並且可以在芯片中放置環路濾波器元件。 顯然,這種方案可以讓設計工程師簡化他們的工作。

為了獲得GSM系統所需的發射機功率控制,PA廠商一般都在功率放大器模塊(PAM)中包含了這個功能。 電源控制器通常由多達數千個數字 CMOS 門組成,這些門在 PAM 中製作在一個獨立的芯片中。 該要素將使 PAM 的成本增加 0.30 美元~0.40 美元。 將此功能集成到 RF 設備中將使 GaAs PAM 製造商無需購買數字 CMOS 電路並將其安裝到 PAM 中。 對於每月生產數以千計產品的 OEM 來說,移除這個冗餘組件將大大降低他們的成本。

高級集成可以帶來大量節省的另一個領域是 VCXO。 過去,昂貴的 vctcxo 模塊是在 RF 設備中作為分立元件購買和設計的。 因此,將 vctcxo 模塊的通用組件集成到 RF 設備中可以降低成本和相關的設計問題。 使用trf6151,只需要一個低成本的晶振和變容二極管就可以完成vctcxo的功能。

儘管有這些集成和設計簡化,RF 設計工程師仍然面臨艱難的選擇,其中之一是輸入靈敏度和 Rx 功耗。 眾所周知,低噪聲放大器(LNA)設計中使用的電流越大,整體噪聲特性越低。 設計工程師必須確定接收器的總功率預算和接收器的靈敏度等級要求。 但是,噪聲不會隨著功率的降低而降低。 事實上,情況恰恰相反。 因此,雖然它可以滿足GSM標準規範,但設計人員必須經常問自己是否值得為達到一定的靈敏度水平而在功耗上付出代價。 這個問題也解釋了為什麼設計工程師和IC製造商在整個設計過程中需要密切合作。 設計工程師的反饋可以指導 IC 製造商在開發未來的射頻產品時更好地服務於無線行業。

向SOC發展

降低無線系統的成本、功耗和復雜性對於成功滿足系統集成的要求非常重要。 然而,開發手機高集成度解決方案需要半導體行業克服複雜的技術障礙。 其中一些障礙很少為設計人員所關注,因為他們中的許多人並不想知道 SOC 器件是如何製造的,只要它能夠提供所需的性能即可。 因此,有必要快速了解一些工藝技術,這些技術會影響手機集成中使用的設備的能力和可用性。

手機射頻電子系統的集成有幾種可行的方案。 首先,可以使用傳統技術在相對簡單的雙極或 BiCMOS 工藝中實現傳統的 RF 架構。 最終的射頻芯片可以使用多芯片封裝技術(系統級封裝技術)與手機數字邏輯功能組裝在一起。 雖然這項技術有很多優點,例如使用熟悉的射頻設計方法和成熟的工藝和技術,但由於測試設備的成本和良率較高,很難商業化。

此外,手機電子系統的集成也可以通過先進的BiCMOS(SiGe)晶圓工藝獲得。 然而,由於 SiGe HBT 器件的加工需要額外的光刻工藝,最終的芯片將需要額外的成本。 同時,由於SiGe BiCMOS工藝無法使用最先進的光刻工藝,BiCMOS工藝通常落後於先進的數字CMOS工藝。 這些都會給手機增加特性和降低成本帶來巨大壓力。 它無法通過簡單的晶圓工藝策略解決,因為該技術無法始終將系統邏輯或數字部分保持在盡可能低的價格。 因此,將系統基帶功能射頻部分單片集成在 BiCMOS(或 SiGe)中並不是一個好的選擇。

可以考慮的最終解決方案是 CMOS 中的 RF 集成,這也面臨著相當大的挑戰。 儘管有多種 CMOS 蜂窩射頻設計,但這些設計主要基於模擬功能。 CMOS技術難以實現模擬混頻器、濾波器和放大器,功耗一般大於SiGe BiCMOS方案。 隨著工藝技術的發展,CMOS的額定等級越來越低,這使得模擬設計變得更加困難。 在開發新工藝的初期,器件建模和工藝成熟度一般不能滿足模擬模塊設計所需的高精度參數建模要求。 然而,最近開發的數字 CMOS RF 架構使單片 CMOS 集成更具吸引力。

隨著製造商尋求低成本射頻系統級芯片解決方案,這些解決方案也推動了半導體行業的發展。 雖然每種集成方案都有難度,但射頻元件集成度能達到如此高的水平,確實令人驚訝。 克服這些困難將使無線手機的設計向前邁出一大步,並為不久的將來更大程度的集成指明方向。

本文結論

RF集成還存在很多困難。 現代手機的每個射頻設備都面臨著嚴格的性能要求。 靈敏度要求約為–106dbm(106MW以下1db)或更高,對應的電平只有幾微伏; 另外,選擇性,即有用信道對相鄰頻段的抑制能力(俗稱阻塞),應在60dB左右; 此外,系統振盪器需要在極低的相位噪聲下工作,以防止折疊阻塞能量進入接收帶。 由於頻率非常高且性能要求極其苛刻,因此射頻集成非常困難。

處理多頻率標准給整個SOC頻率帶來了真正的挑戰。 希望減少帶內信號傳輸產生的激勵。 數字射頻集成的內容遠不止將多個射頻組件放在一個芯片中。 需要一種新的硬件共享架構。

對於系統設計人員來說,目前簡單、高度集成且具有成本效益的半導體器件可以大大降低設計複雜度。 同時,它們可以豐富無線設備的特性,保持系統尺寸、電池壽命和成本不變。 新的高度集成的射頻器件還可以消除無線設計中的一些爭議,節省工程師的寶貴時間。