- 06

- Oct

Kurangi jumlah komponen dan kurangi area papan sirkuit melalui integrasi RF nirkabel

Kurangi jumlah komponen dan kurangi area papan sirkuit melalui integrasi RF nirkabel

Pada perangkat nirkabel saat ini, lebih dari setengah komponen pada papan sirkuit adalah perangkat RF analog. Oleh karena itu, cara yang efektif untuk mengurangi area papan sirkuit dan konsumsi daya adalah dengan melakukan integrasi RF yang lebih besar dan mengembangkan chip tingkat sistem. Makalah ini memperkenalkan status pengembangan integrasi RF, dan mengajukan beberapa tindakan pencegahan dan solusi untuk beberapa masalah ini.

Beberapa tahun yang lalu, pasar telepon seluler didominasi oleh telepon single-mode single band dan dual band, dan teknologi yang digunakan hanya??? Tahan satu atau dua pita seluler semuanya??? Metode modulasi yang sama, skema akses multi-saluran dan protokol diadopsi dalam pita frekuensi holding. Sebaliknya, desain ponsel generasi baru saat ini jauh lebih kompleks dan dapat menyediakan multi-band dan multi-mode??? Ini memiliki jaringan area pribadi Bluetooth, penentuan posisi GPS dan fungsi lainnya, dan fungsi penerimaan UWB dan TV mulai muncul. Selain itu, aplikasi seperti game, gambar, audio dan video telah menjadi sangat umum di ponsel.

Telepon nirkabel menjadi perangkat kompleks yang disebut pusat hiburan pribadi genggam. Tren perkembangannya terus membawa lebih banyak tantangan bagi para desainer. Meskipun dibandingkan dengan ponsel dengan hanya fungsi suara, generasi baru ponsel telah meningkat secara signifikan dalam pemrosesan komunikasi, pemrosesan aplikasi, jumlah antarmuka RF dan kapasitas memori terintegrasi, pengguna masih mengharapkan ponsel memiliki volume yang lebih kecil, bentuk yang ramping, rendah harga dan tampilan warna yang besar, dapat memberikan waktu siaga dan bicara yang mirip dengan telepon suara tradisional. Mempertahankan ukuran keseluruhan dan konsumsi daya yang ada, tetapi membuat fungsi meningkat secara eksponensial, sambil mempertahankan biaya sistem secara keseluruhan tidak berubah, semua ini menimbulkan banyak masalah bagi perancang sistem.

Jelas, masalahnya melibatkan semua bagian dari keseluruhan desain sistem, serta pemasok semua konten komunikasi dan hiburan nirkabel. Salah satu area yang sangat efektif dalam mengurangi area papan dan konsumsi daya adalah bagian RF dari desain sistem nirkabel. Ini karena pada ponsel biasa saat ini, lebih dari setengah komponen di papan adalah komponen RF analog, yang bersama-sama mencakup 30-40% dari seluruh area papan, seperti sistem Bluetooth RF seperti GPS dan WLAN juga akan sangat meningkatkan kebutuhan ruang.

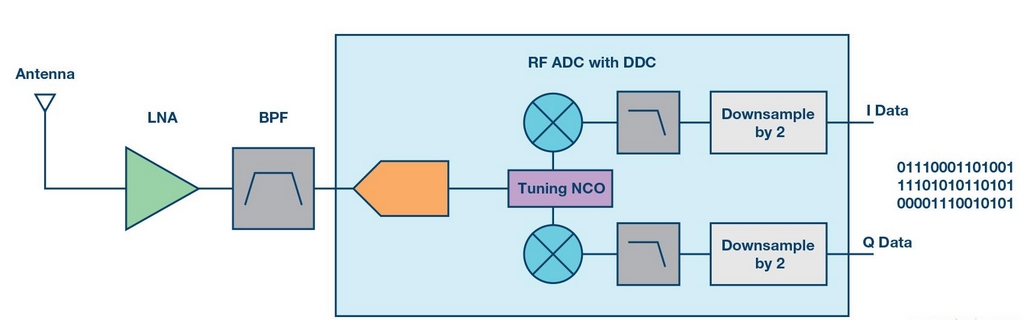

Solusinya adalah melakukan integrasi RF skala besar dan akhirnya berkembang menjadi chip level sistem yang terintegrasi penuh. Beberapa desainer menempatkan konverter analog-ke-digital ke antena untuk mengurangi total ruang papan sirkuit yang diperlukan untuk fungsi RF. Ketika teknologi integrasi semikonduktor dapat mengintegrasikan lebih banyak fungsi dalam satu perangkat, jumlah perangkat diskrit dan ruang papan sirkuit yang digunakan untuk mengakomodasi perangkat ini akan berkurang. Saat industri bergerak menuju integrasi chip tingkat sistem, desainer akan terus menemukan teknologi baru untuk memenuhi kontradiksi antara kompleksitas RF yang lebih tinggi dan masa pakai baterai yang lebih lama pada perangkat nirkabel kecil.

Status pengembangan integrasi RF

Perkembangan penting integrasi RF muncul sekitar dua tahun lalu. Pada saat itu, perkembangan teknologi RF dan modem pita dasar digital memungkinkan untuk menggantikan perangkat RF superheterodyne dengan penerima konversi turun langsung di telepon seluler nirkabel. Perangkat RF superheterodyne menggunakan multistage mixer, filter, dan osilator terkontrol tegangan ganda (VCO), yang telah digunakan dengan baik selama bertahun-tahun, tetapi integrasi perangkat RF konversi frekuensi langsung dapat sangat mengurangi jumlah total komponen RF GSM. Pada akhir 1990-an, subsistem RF superheterodyne pita tunggal yang khas termasuk PA, sakelar antena, LDO, RF sinyal kecil, dan vctcxo, yang membutuhkan sekitar 200 perangkat terpisah; Hari ini, kita dapat merancang sistem konversi frekuensi langsung dengan fungsi empat pita, yang mengintegrasikan filter loop VCO, VCXO dan PLL, tetapi jumlah komponennya kurang dari 50. Gambar 1: Transceiver GSM empat pita dengan integrasi tinggi.

Misalnya, transceiver trf6151 (Gambar 1) Texas Instruments untuk GSM termasuk pengatur tegangan on-chip, saluran VCO dan VCO, kontrol daya PA, deteksi pemblokir tepi filter loop PLL, kontrol langkah demi langkah penguatan LNA dan VCXO.

Untuk desainer, integrasi lanjutan membantu mengatasi beberapa masalah utama dalam RF nirkabel, di antaranya yang paling mendasar adalah catu daya DC dan regulasi transceiver. Selama panggilan, tegangan baterai akan berubah dengan perubahan suhu dan waktu. Selain itu, noise coupling dari catu daya TX VCO dan Rx VCO juga akan mempengaruhi kinerja sistem secara keseluruhan. Oleh karena itu, perancang dihadapkan pada masalah bagaimana memecahkan regulator papan sirkuit RF dan sebagian besar komponen pasif terkait. Mengintegrasikan perangkat ini ke dalam transceiver RF berarti bahwa satu-satunya komponen eksternal yang diperlukan adalah kapasitor decoupling sederhana, yang terhubung langsung ke catu daya, yang tidak hanya menyederhanakan desain, tetapi juga menghemat ruang papan sirkuit.

Tantangan lain bagi perancang RF adalah rentang penyetelan VCO dan waktu penguncian. Dalam semua desain VCO analog. Karena seringkali perlu untuk menyeimbangkan waktu penguncian dan rentang penyetelan, filter loop biasanya ditempatkan di luar chip. Terkadang, ini dapat diselesaikan dalam kontrol perangkat lunak rentang penyetelan VCO. Namun, metode ini mengedepankan kebutuhan sumber daya tambahan untuk pengembangan telepon secara keseluruhan. Ketika fungsi penyetelan digital disertakan dalam VCO dan dapat memberikan kalibrasi sendiri, rentang penyetelan yang diperluas dapat diperoleh, dan elemen filter loop dapat ditempatkan di dalam chip. Jelas, skema ini dapat memungkinkan insinyur desain untuk menyederhanakan pekerjaan mereka.

Untuk mendapatkan kontrol daya pemancar yang diperlukan oleh sistem GSM, pabrikan PA umumnya menyertakan fungsi ini dalam modul penguat daya (PAM). Pengontrol daya biasanya terdiri dari hingga ribuan gerbang CMOS digital, yang dibuat dalam chip independen di PAM. Elemen ini akan meningkatkan biaya PAM sebesar US $0.30 ~ 0.40. Mengintegrasikan fungsi ini ke dalam perangkat RF akan memungkinkan produsen PAM GaAs untuk tidak membeli sirkuit CMOS digital dan memasangnya ke PAM. Untuk OEM yang memproduksi ribuan produk setiap bulan, menghapus komponen yang berlebihan ini akan sangat mengurangi biayanya.

Area lain di mana integrasi lanjutan dapat menghasilkan penghematan besar adalah VCXO. Di masa lalu, modul vctcxo yang mahal dibeli dan dirancang dalam perangkat RF sebagai komponen terpisah. Oleh karena itu, menggabungkan komponen umum modul vctcxo ke dalam perangkat RF dapat mengurangi biaya dan masalah desain terkait. Menggunakan trf6151, hanya kristal dan varactor murah yang diperlukan untuk menyelesaikan fungsi vctcxo.

Terlepas dari integrasi dan penyederhanaan desain ini, insinyur desain RF masih menghadapi pilihan yang sulit, salah satunya adalah sensitivitas input dan konsumsi daya Rx. Diketahui bahwa semakin besar arus yang digunakan dalam desain penguat kebisingan rendah (LNA), semakin rendah karakteristik kebisingan secara keseluruhan. Insinyur desain harus menentukan total anggaran daya penerima dan persyaratan tingkat sensitivitas penerima. Namun, kebisingan tidak berkurang dengan pengurangan daya. Faktanya, itu adalah kebalikannya. Oleh karena itu, meskipun dapat memenuhi spesifikasi standar GSM, desainer harus sering bertanya pada diri sendiri apakah layak membayar harga dalam konsumsi daya untuk mencapai tingkat sensitivitas tertentu. Pertanyaan ini juga menjelaskan mengapa perlu bagi insinyur desain dan produsen IC untuk bekerja sama secara erat dalam keseluruhan proses desain. Umpan balik dari insinyur desain dapat memandu produsen IC untuk melayani industri nirkabel dengan lebih baik saat mengembangkan produk RF di masa mendatang.

Berkembang menuju SOC

Mengurangi biaya, daya dan kompleksitas sistem nirkabel sangat penting untuk berhasil memenuhi persyaratan integrasi sistem. Namun, pengembangan solusi integrasi tinggi untuk ponsel membutuhkan industri semikonduktor untuk mengatasi hambatan teknis yang kompleks. Beberapa kendala tersebut jarang diperhatikan oleh para desainer, karena banyak dari mereka yang tidak ingin mengetahui bagaimana perangkat SOC dibuat, asalkan dapat memberikan performa yang dibutuhkan. Oleh karena itu, diperlukan pemahaman yang cepat tentang beberapa teknologi proses, yang akan mempengaruhi kemampuan dan ketersediaan perangkat yang digunakan dalam integrasi telepon seluler.

Ada beberapa skema yang layak untuk integrasi sistem elektronik RF ponsel. Pertama, arsitektur RF tradisional dapat diimplementasikan dalam proses bipolar atau BiCMOS yang relatif sederhana menggunakan teknologi tradisional. Chip RF akhir dapat dirakit dengan fungsi logika digital ponsel menggunakan teknologi pengemasan multi chip (teknologi pengemasan tingkat sistem). Meskipun teknologi ini memiliki banyak keuntungan, seperti menggunakan metode desain RF yang sudah dikenal serta proses dan teknologi yang matang, sulit untuk dikomersialkan karena tingginya biaya dan hasil perangkat uji.

Selain itu, integrasi sistem elektronik ponsel juga dapat diperoleh melalui proses wafer BiCMOS (SiGe) yang canggih. Namun, karena pemrosesan perangkat SiGe HBT membutuhkan proses litografi tambahan, chip akhir akan membutuhkan biaya tambahan. Pada saat yang sama, karena teknologi SiGe BiCMOS tidak dapat menggunakan proses litografi yang paling canggih, proses BiCMOS biasanya tertinggal dari proses CMOS digital yang canggih. Ini akan membawa tekanan besar untuk meningkatkan karakteristik ponsel dan mengurangi biaya. Ini tidak dapat diselesaikan dengan strategi proses wafer yang sederhana, karena teknologi ini tidak dapat menjaga logika sistem atau bagian digital pada harga serendah mungkin setiap saat. Oleh karena itu, integrasi monolitik bagian RF fungsi pita dasar sistem di BiCMOS (atau SiGe) bukanlah pilihan yang baik.

Solusi terakhir yang dapat dipertimbangkan adalah integrasi RF dalam CMOS, yang juga menghadapi banyak tantangan. Meskipun ada beberapa desain RF seluler CMOS, desain ini sebagian besar didasarkan pada fungsi analog. Sulit untuk mengimplementasikan mixer analog, filter dan amplifier dengan teknologi CMOS, dan konsumsi daya umumnya lebih besar daripada skema SiGe BiCMOS. Dengan perkembangan teknologi proses, tingkat pengenal CMOS semakin rendah, yang membuat desain analog semakin sulit. Pada tahap awal pengembangan proses baru, pemodelan perangkat dan kematangan proses umumnya tidak dapat memenuhi persyaratan pemodelan parameter presisi tinggi yang diperlukan untuk desain modul analog. Namun, arsitektur RF CMOS digital yang baru-baru ini dikembangkan membuat integrasi CMOS monolitik lebih menarik.

Solusi ini juga mendorong industri semikonduktor karena produsen mencari solusi chip tingkat sistem RF berbiaya rendah. Meskipun setiap skema integrasi memiliki kesulitan, sungguh mengejutkan bahwa integrasi komponen RF dapat mencapai tingkat yang begitu tinggi. Mengatasi kesulitan ini akan mengambil langkah maju yang besar dalam desain ponsel nirkabel dan menetapkan arah untuk integrasi yang lebih besar dalam waktu dekat.

Kesimpulan dari makalah ini

Masih banyak kesulitan dalam integrasi RF. Setiap perangkat RF ponsel modern dihadapkan pada persyaratan kinerja yang ketat. Persyaratan sensitivitas sekitar – 106dbm (106db di bawah 1 MW) atau lebih tinggi, dan tingkat yang sesuai hanya beberapa mikrovolt; Selain itu, selektivitas, yaitu kemampuan penolakan saluran yang berguna ke pita frekuensi yang berdekatan (biasanya disebut sebagai pemblokiran), harus berada di urutan 60dB; Selain itu, osilator sistem diperlukan untuk beroperasi di bawah kebisingan fase yang sangat rendah untuk mencegah energi pemblokiran lipat memasuki pita penerima. Integrasi RF sangat sulit karena frekuensi yang sangat tinggi dan persyaratan kinerja yang sangat menuntut.

Memproses standar multi frekuensi menghadirkan tantangan nyata bagi seluruh frekuensi SOC. Diharapkan dapat mengurangi eksitasi yang ditimbulkan oleh transmisi sinyal in band. Isi integrasi RF digital lebih dari sekadar menempatkan beberapa komponen RF dalam satu chip. Diperlukan arsitektur baru untuk berbagi perangkat keras.

Untuk perancang sistem, perangkat semikonduktor yang sederhana, sangat terintegrasi, dan hemat biaya saat ini dapat sangat mengurangi kerumitan desain. Pada saat yang sama, mereka dapat memperkaya karakteristik perangkat nirkabel dan menjaga ukuran sistem, masa pakai baterai, dan biaya tidak berubah. Perangkat RF baru yang sangat terintegrasi juga dapat menghilangkan beberapa perselisihan dalam desain nirkabel dan menghemat waktu berharga para insinyur.