- 06

- Oct

Giảm số lượng linh kiện và giảm diện tích bảng mạch thông qua tích hợp RF không dây

Giảm số lượng thành phần và giảm diện tích bảng mạch thông qua tích hợp RF không dây

Trong các thiết bị không dây ngày nay, hơn một nửa thành phần trên bảng mạch là thiết bị RF tương tự. Do đó, một cách hiệu quả để giảm diện tích bảng mạch và tiêu thụ điện năng là thực hiện tích hợp RF quy mô lớn hơn và phát triển theo hướng chip cấp hệ thống. Bài báo này giới thiệu tình hình phát triển của tích hợp RF và đưa ra một số biện pháp đối phó và giải pháp cho một số vấn đề này.

Một vài năm trước, thị trường điện thoại di động bị thống trị bởi điện thoại đơn chế độ băng tần đơn và băng tần kép, và công nghệ được sử dụng chỉ là ??? Giữ một hoặc hai băng tần di động trong tất cả ??? Cùng một phương pháp điều chế, sơ đồ truy cập đa kênh và giao thức được áp dụng trong dải tần số đang giữ. Ngược lại, thiết kế của thế hệ điện thoại di động mới ngày nay phức tạp hơn nhiều và có thể cung cấp đa băng tần và đa chế độ ??? Nó có mạng khu vực cá nhân Bluetooth, định vị GPS và các chức năng khác, UWB và chức năng nhận TV đã bắt đầu xuất hiện. Ngoài ra, các ứng dụng như trò chơi, hình ảnh, âm thanh và video đã trở nên rất phổ biến trong điện thoại di động.

Điện thoại không dây đang trở thành một thiết bị phức tạp được gọi là trung tâm giải trí cá nhân cầm tay. Xu hướng phát triển của nó tiếp tục mang đến nhiều thách thức hơn cho các nhà thiết kế. Mặc dù so với điện thoại di động chỉ có chức năng thoại, điện thoại di động thế hệ mới đã tăng lên đáng kể về xử lý giao tiếp, xử lý ứng dụng, số lượng giao diện RF và dung lượng bộ nhớ tích hợp, người dùng vẫn mong muốn điện thoại di động có âm lượng nhỏ hơn, hình dáng tinh gọn, thấp giá và màn hình màu lớn, Nó có thể cung cấp thời gian chờ và đàm thoại tương tự như điện thoại thoại truyền thống. Duy trì kích thước tổng thể hiện có và mức tiêu thụ điện năng, nhưng làm cho chức năng tăng lên theo cấp số nhân, trong khi duy trì chi phí hệ thống tổng thể không đổi, tất cả những điều này đặt ra rất nhiều vấn đề cho các nhà thiết kế hệ thống.

Rõ ràng, vấn đề liên quan đến tất cả các phần của thiết kế toàn bộ hệ thống, cũng như các nhà cung cấp tất cả các nội dung giải trí và truyền thông không dây. Một lĩnh vực đặc biệt hiệu quả trong việc giảm diện tích bo mạch và tiêu thụ điện năng là phần RF của thiết kế hệ thống không dây. Điều này là do trong điện thoại di động điển hình ngày nay, hơn một nửa số thành phần trên bo mạch là các thành phần RF tương tự, chúng cùng nhau chiếm 30 – 40% diện tích toàn bộ bo mạch, chẳng hạn như các hệ thống Bluetooth RF như GPS và WLAN cũng sẽ rất lớn. tăng yêu cầu về không gian.

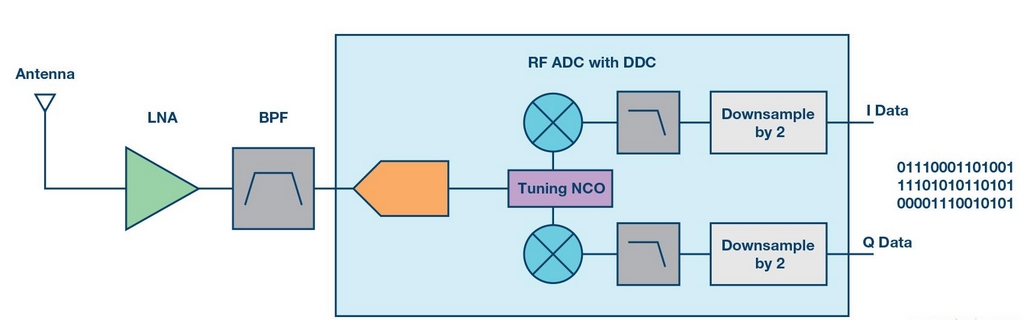

Giải pháp là thực hiện tích hợp RF quy mô lớn hơn và cuối cùng là phát triển thành chip cấp hệ thống tích hợp đầy đủ. Một số nhà thiết kế đặt bộ chuyển đổi tương tự sang kỹ thuật số vào ăng-ten để giảm tổng không gian bảng mạch cần thiết cho các chức năng RF. Khi công nghệ tích hợp bán dẫn có thể tích hợp nhiều chức năng hơn trong một thiết bị duy nhất, số lượng thiết bị rời và không gian bảng mạch được sử dụng để chứa các thiết bị này sẽ giảm theo. Khi ngành công nghiệp tiến tới tích hợp chip cấp hệ thống, các nhà thiết kế sẽ tiếp tục tìm ra các công nghệ mới để đáp ứng mâu thuẫn giữa độ phức tạp RF cao hơn và thời lượng pin dài hơn trong các thiết bị không dây nhỏ.

Tình trạng phát triển của tích hợp RF

Một sự phát triển quan trọng của tích hợp RF đã xuất hiện khoảng hai năm trước. Vào thời điểm đó, sự phát triển của công nghệ RF và modem băng tần cơ sở kỹ thuật số đã làm cho nó có thể thay thế các thiết bị RF superheterodyne bằng máy thu chuyển đổi trực tiếp trong điện thoại di động không dây. Thiết bị RF Superheterodyne sử dụng bộ trộn đa tầng, bộ lọc và nhiều bộ dao động điều khiển điện áp (VCO), đã được sử dụng phổ biến trong nhiều năm, nhưng việc tích hợp các thiết bị RF chuyển đổi tần số trực tiếp có thể làm giảm đáng kể tổng số thành phần GSM RF. Vào cuối những năm 1990, một hệ thống con RF superheterodyne một băng tần điển hình bao gồm PA, công tắc ăng ten, LDO, RF tín hiệu nhỏ và vctcxo, yêu cầu khoảng 200 thiết bị rời; Ngày nay, chúng ta có thể thiết kế một hệ thống chuyển đổi tần số trực tiếp với chức năng bốn băng tần, tích hợp bộ lọc vòng VCO, VCXO và PLL, nhưng số thành phần của nó ít hơn 50. Hình 1: Bộ thu phát GSM bốn băng tần với khả năng tích hợp cao.

Ví dụ, bộ thu phát trf6151 (Hình 1) của Texas Instruments dành cho GSM bao gồm bộ điều chỉnh điện áp trên chip, kênh VCO và VCO, điều khiển công suất PA, phát hiện bộ chặn cạnh bộ lọc vòng PLL, điều khiển từng bước độ lợi LNA và VCXO.

Đối với các nhà thiết kế, tích hợp nâng cao giúp khắc phục một số vấn đề lớn trong RF không dây, trong đó vấn đề cơ bản nhất là nguồn điện DC và điều chỉnh của bộ thu phát. Trong khi gọi, điện áp của pin sẽ thay đổi theo sự thay đổi của nhiệt độ và thời gian. Ngoài ra, việc ghép nhiễu từ bộ nguồn TX VCO và Rx VCO cũng sẽ ảnh hưởng đến hiệu suất của toàn hệ thống. Do đó, các nhà thiết kế đang phải đối mặt với vấn đề làm thế nào để giải quyết bộ điều chỉnh bảng mạch RF và hầu hết các thành phần thụ động liên quan. Tích hợp các thiết bị này vào bộ thu phát RF có nghĩa là thành phần bên ngoài duy nhất cần có là một tụ điện tách rời đơn giản, được kết nối trực tiếp với nguồn điện, không chỉ đơn giản hóa thiết kế mà còn tiết kiệm không gian bảng mạch.

Một thách thức khác đối với các nhà thiết kế RF là phạm vi điều chỉnh VCO và thời gian khóa. Trong tất cả các thiết kế VCO tương tự. Vì thường phải cân bằng giữa thời gian khóa và phạm vi điều chỉnh, bộ lọc vòng lặp thường được đặt bên ngoài chip. Đôi khi, điều này có thể được giải quyết trong phần mềm điều khiển dải điều chỉnh VCO. Tuy nhiên, phương pháp này đặt ra các yêu cầu về tài nguyên bổ sung cho sự phát triển chung của điện thoại. Khi chức năng điều chỉnh kỹ thuật số được bao gồm trong VCO và có thể tự hiệu chuẩn, có thể thu được dải điều chỉnh mở rộng và phần tử lọc vòng lặp có thể được đặt trong chip. Rõ ràng, chương trình này có thể cho phép các kỹ sư thiết kế đơn giản hóa công việc của họ.

Để có được điều khiển công suất máy phát theo yêu cầu của hệ thống GSM, các nhà sản xuất PA thường bao gồm chức năng này trong mô-đun khuếch đại công suất (PAM). Bộ điều khiển nguồn thường bao gồm hàng nghìn cổng CMOS kỹ thuật số, được tạo ra trong một chip độc lập trong PAM. Yếu tố này sẽ làm tăng chi phí của PAM thêm US $ 0.30 ~ 0.40. Việc tích hợp chức năng này vào các thiết bị RF sẽ cho phép các nhà sản xuất GaAs PAM không phải mua các mạch CMOS kỹ thuật số và cài đặt chúng vào PAM. Đối với một OEM sản xuất hàng nghìn sản phẩm mỗi tháng, việc loại bỏ thành phần dư thừa này sẽ giúp giảm chi phí của họ rất nhiều.

Một lĩnh vực khác mà tích hợp nâng cao có thể mang lại tiết kiệm đáng kể là VCXO. Trong quá khứ, các mô-đun vctcxo đắt tiền được mua và thiết kế trong các thiết bị RF dưới dạng các thành phần rời rạc. Do đó, việc kết hợp các thành phần chung của mô-đun vctcxo vào thiết bị RF có thể giảm chi phí và các vấn đề thiết kế liên quan. Sử dụng trf6151, chỉ cần một tinh thể và varactor giá rẻ để hoàn thành chức năng của vctcxo.

Bất chấp sự tích hợp và đơn giản hóa thiết kế này, các kỹ sư thiết kế RF vẫn phải đối mặt với những lựa chọn khó khăn, một trong số đó là độ nhạy đầu vào và mức tiêu thụ điện năng Rx. Ai cũng biết rằng dòng điện được sử dụng trong thiết kế bộ khuếch đại nhiễu thấp (LNA) càng lớn thì đặc tính nhiễu tổng thể càng thấp. Kỹ sư thiết kế phải xác định tổng ngân sách công suất của máy thu và các yêu cầu về mức độ nhạy của máy thu. Tuy nhiên, tiếng ồn không giảm khi giảm công suất. Trong thực tế thì ngược lại. Do đó, mặc dù nó có thể đáp ứng thông số kỹ thuật của tiêu chuẩn GSM, nhưng các nhà thiết kế thường phải tự hỏi mình liệu có đáng phải trả giá trong việc tiêu thụ điện năng để đạt được một mức độ nhạy nhất định hay không. Câu hỏi này cũng giải thích tại sao các kỹ sư thiết kế và nhà sản xuất vi mạch cần phải hợp tác chặt chẽ trong toàn bộ quá trình thiết kế. Phản hồi từ các kỹ sư thiết kế có thể hướng dẫn các nhà sản xuất vi mạch phục vụ tốt hơn cho ngành công nghiệp không dây khi phát triển các sản phẩm RF trong tương lai.

Phát triển theo hướng SOC

Giảm chi phí, điện năng và độ phức tạp của hệ thống không dây là rất quan trọng để đáp ứng thành công các yêu cầu tích hợp hệ thống. Tuy nhiên, sự phát triển của các giải pháp tích hợp cao cho điện thoại di động đòi hỏi ngành công nghiệp bán dẫn phải vượt qua những trở ngại kỹ thuật phức tạp. Một số trở ngại này hiếm khi được các nhà thiết kế quan tâm, bởi vì nhiều người trong số họ không muốn biết các thiết bị SOC được tạo ra như thế nào, Miễn là nó có thể cung cấp hiệu suất cần thiết. Do đó, cần phải hiểu nhanh về một số công nghệ quy trình, điều này sẽ ảnh hưởng đến khả năng và tính khả dụng của các thiết bị được sử dụng trong tích hợp điện thoại di động.

Có một số phương án khả thi để tích hợp hệ thống điện tử RF của điện thoại di động. Thứ nhất, một kiến trúc RF truyền thống có thể được thực hiện trong một quy trình lưỡng cực hoặc BiCMOS tương đối đơn giản bằng cách sử dụng công nghệ truyền thống. Chip RF cuối cùng có thể được lắp ráp với các chức năng logic kỹ thuật số của điện thoại di động bằng cách sử dụng công nghệ đóng gói đa chip (công nghệ đóng gói cấp hệ thống). Mặc dù công nghệ này có nhiều ưu điểm, chẳng hạn như sử dụng các phương pháp thiết kế RF quen thuộc và các quy trình và công nghệ trưởng thành, nhưng rất khó để thương mại hóa do chi phí và năng suất của các thiết bị thử nghiệm cao.

Ngoài ra, việc tích hợp hệ thống điện tử điện thoại di động cũng có thể đạt được nhờ quy trình wafer BiCMOS (SiGe) tiên tiến. Tuy nhiên, vì quá trình xử lý thiết bị SiGe HBT yêu cầu thêm quy trình in thạch bản, chip cuối cùng sẽ yêu cầu thêm một khoản chi phí. Đồng thời, do công nghệ SiGe BiCMOS không thể sử dụng quy trình in thạch bản tiên tiến nhất, quy trình BiCMOS thường chậm hơn quy trình CMOS kỹ thuật số tiên tiến. Những điều này sẽ mang lại áp lực lớn để tăng các đặc tính của điện thoại di động và giảm giá thành. Nó không thể được giải quyết với một chiến lược quy trình wafer đơn giản, bởi vì công nghệ này không thể giữ logic hệ thống hoặc phần kỹ thuật số ở mức giá thấp nhất có thể tại mọi thời điểm. Do đó, tích hợp nguyên khối chức năng băng tần cơ sở của hệ thống phần RF trong BiCMOS (hoặc SiGe) không phải là một lựa chọn tốt.

Giải pháp cuối cùng có thể được xem xét là tích hợp RF trong CMOS, cũng phải đối mặt với những thách thức đáng kể. Mặc dù có một số thiết kế RF di động CMOS, những thiết kế này phần lớn dựa trên các chức năng tương tự. Rất khó triển khai các bộ trộn, bộ lọc và bộ khuếch đại tương tự với công nghệ CMOS, và mức tiêu thụ điện năng nói chung lớn hơn sơ đồ SiGe BiCMOS. Với sự phát triển của công nghệ quy trình, mức đánh giá CMOS ngày càng thấp hơn, điều này làm cho việc thiết kế analog trở nên khó khăn hơn. Trong giai đoạn đầu của việc phát triển các quy trình mới, việc mô hình hóa thiết bị và quá trình hoàn thiện nói chung không thể đáp ứng các yêu cầu của mô hình thông số có độ chính xác cao cần thiết cho thiết kế mô-đun tương tự. Tuy nhiên, kiến trúc CMOS RF kỹ thuật số được phát triển gần đây làm cho việc tích hợp CMOS nguyên khối trở nên hấp dẫn hơn.

Các giải pháp này cũng thúc đẩy ngành công nghiệp bán dẫn khi các nhà sản xuất tìm kiếm các giải pháp chip cấp hệ thống RF chi phí thấp. Mặc dù mỗi sơ đồ tích hợp đều có những khó khăn, nhưng thực sự đáng ngạc nhiên là sự tích hợp thành phần RF có thể đạt đến mức cao như vậy. Vượt qua những khó khăn này sẽ tạo ra một bước tiến lớn trong thiết kế điện thoại di động không dây và đặt ra hướng tích hợp lớn hơn trong tương lai gần.

Kết luận của bài báo này

Vẫn còn nhiều khó khăn trong việc tích hợp RF. Mỗi thiết bị RF của điện thoại di động hiện đại đều phải đối mặt với các yêu cầu hiệu suất nghiêm ngặt. Yêu cầu về độ nhạy là khoảng – 106dbm (106db dưới 1 MW) hoặc cao hơn, và mức tương ứng chỉ là một vài microvolt; Ngoài ra, độ chọn lọc, nghĩa là, khả năng loại bỏ của kênh hữu ích đối với dải tần lân cận (thường được gọi là chặn), phải theo thứ tự 60dB; Ngoài ra, bộ tạo dao động của hệ thống được yêu cầu hoạt động dưới nhiễu pha rất thấp để ngăn chặn năng lượng chặn gấp vào băng tần nhận. Việc tích hợp RF là rất khó vì tần số rất cao và các yêu cầu về hiệu suất cực kỳ khắt khe.

Xử lý tiêu chuẩn đa tần số mang đến một thách thức thực sự cho toàn bộ tần số SOC. Nó được hy vọng để giảm kích thích được tạo ra trong quá trình truyền tín hiệu băng tần. Nội dung của tích hợp RF kỹ thuật số nhiều hơn là đặt nhiều thành phần RF trong một chip. Một kiến trúc chia sẻ phần cứng mới là cần thiết.

Đối với các nhà thiết kế hệ thống, các thiết bị bán dẫn đơn giản, tích hợp cao và hiệu quả về chi phí hiện nay có thể làm giảm đáng kể độ phức tạp của thiết kế. Đồng thời, chúng có thể làm phong phú thêm các đặc tính của thiết bị không dây và giữ nguyên kích thước hệ thống, thời lượng pin và chi phí. Các thiết bị RF tích hợp cao mới cũng có thể loại bỏ một số tranh chấp trong thiết kế không dây và tiết kiệm thời gian quý báu của các kỹ sư.