- 06

- Oct

घटकांची संख्या कमी करा आणि वायरलेस आरएफ एकत्रीकरणाद्वारे सर्किट बोर्डचे क्षेत्र कमी करा

घटकांची संख्या कमी करा आणि चे क्षेत्र कमी करा सर्किट बोर्ड वायरलेस आरएफ एकत्रीकरणाद्वारे

आजच्या वायरलेस उपकरणांमध्ये, सर्किट बोर्डवरील अर्ध्याहून अधिक घटक अॅनालॉग आरएफ डिव्हाइसेस आहेत. म्हणूनच, सर्किट बोर्ड क्षेत्र आणि विजेचा वापर कमी करण्याचा एक प्रभावी मार्ग म्हणजे मोठ्या प्रमाणावर आरएफ एकीकरण करणे आणि सिस्टम लेव्हल चिपच्या दिशेने विकसित करणे. हा पेपर आरएफ एकत्रीकरणाच्या विकास स्थितीचा परिचय करून देतो आणि यापैकी काही समस्यांवर काही उपाययोजना आणि उपाय पुढे ठेवतो.

काही वर्षांपूर्वी, सेल्युलर फोन बाजारात सिंगल बँड आणि ड्युअल बँड सिंगल-मोड फोनचे वर्चस्व होते आणि वापरलेले तंत्रज्ञान फक्त ??? एक किंवा दोन सेल्युलर बँड धरा ??? होल्डिंग फ्रिक्वेंसी बँडमध्ये समान मॉड्यूलेशन पद्धत, मल्टी-चॅनेल प्रवेश योजना आणि प्रोटोकॉल स्वीकारला जातो. याउलट, आजच्या नवीन पिढीच्या सेल्युलर फोनचे डिझाईन अधिक गुंतागुंतीचे आहे आणि ते मल्टी बँड आणि मल्टी-मोड प्रदान करू शकतात ??? यात ब्लूटूथ पर्सनल एरिया नेटवर्क, जीपीएस पोजिशनिंग आणि इतर फंक्शन्स आहेत आणि यूडब्ल्यूबी आणि टीव्ही रिसीव्हिंग फंक्शन्स दिसू लागले आहेत. याव्यतिरिक्त, मोबाइल फोनमध्ये गेम्स, इमेज, ऑडिओ आणि व्हिडीओ सारखे अॅप्लिकेशन खूप सामान्य झाले आहेत.

वायरलेस टेलिफोन एक जटिल उपकरण बनत आहे ज्याला हँडहेल्ड पर्सनल एंटरटेनमेंट सेंटर म्हणतात. त्याच्या विकासाचा कल डिझायनर्सना अधिक आव्हाने आणत आहे. केवळ व्हॉईस फंक्शन असलेल्या मोबाईल फोनच्या तुलनेत, मोबाइल फोनच्या नवीन पिढीने कम्युनिकेशन प्रोसेसिंग, अॅप्लिकेशन प्रोसेसिंग, आरएफ इंटरफेसची संख्या आणि इंटिग्रेटेड मेमरी कॅपेसिटीमध्ये लक्षणीय वाढ केली आहे, तरीही वापरकर्त्यांना मोबाईल फोनची व्हॉल्यूम लहान, सुव्यवस्थित आकार, कमी असणे अपेक्षित आहे. किंमत आणि मोठे रंग प्रदर्शन, हे स्टँडबाय आणि टॉक टाइम पारंपारिक व्हॉईस फोन प्रमाणेच प्रदान करू शकते. विद्यमान एकूण आकार आणि विजेचा वापर राखणे, परंतु कार्यक्षमतेत वाढ करणे, संपूर्ण प्रणालीचा खर्च अपरिवर्तित ठेवताना, या सर्व प्रणाली डिझायनर्सना खूप समस्या निर्माण करतात.

स्पष्टपणे, समस्येमध्ये संपूर्ण सिस्टम डिझाइनचे सर्व भाग तसेच सर्व वायरलेस कम्युनिकेशन आणि मनोरंजन सामग्रीचे पुरवठादार समाविष्ट आहेत. बोर्ड क्षेत्र आणि विजेचा वापर कमी करण्यासाठी विशेषतः प्रभावी असलेले एक क्षेत्र म्हणजे वायरलेस सिस्टम डिझाइनचा आरएफ भाग. याचे कारण असे की आजच्या ठराविक मोबाईल फोनमध्ये, बोर्डवरील अर्ध्याहून अधिक घटक अॅनालॉग आरएफ घटक आहेत, जे एकत्रितपणे संपूर्ण बोर्ड क्षेत्राच्या 30-40% असतात, जसे की ब्लूटूथ आरएफ सिस्टम जसे की जीपीएस आणि डब्ल्यूएलएएन देखील मोठ्या प्रमाणात जागेची आवश्यकता वाढवा.

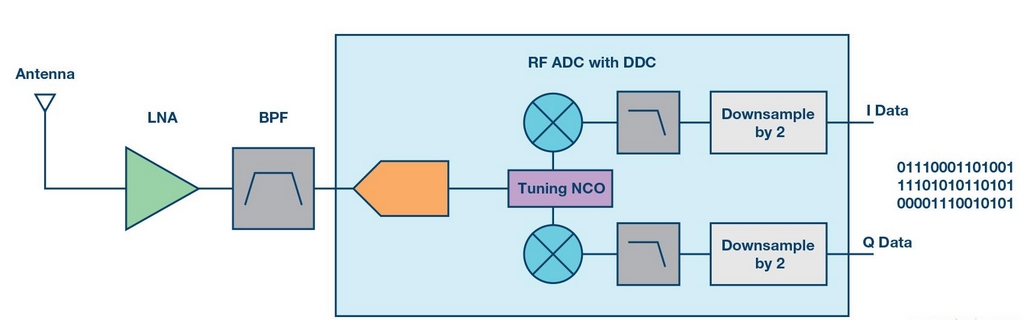

अधिक मोठ्या प्रमाणावर आरएफ एकत्रीकरण करणे आणि शेवटी पूर्णपणे एकात्मिक प्रणाली स्तरीय चिप मध्ये विकसित करणे हा उपाय आहे. आरएफ फंक्शन्ससाठी आवश्यक एकूण सर्किट बोर्ड स्पेस कमी करण्यासाठी काही डिझायनर्स अॅनालॉग ते डिजिटल कन्व्हर्टर्स अँटेनामध्ये टाकतात. जेव्हा सेमीकंडक्टर इंटिग्रेशन टेक्नॉलॉजी एकाच डिव्हाइसमध्ये अधिक फंक्शन्स समाकलित करू शकते, तेव्हा या उपकरणांना सामावून घेण्यासाठी वापरल्या जाणाऱ्या स्वतंत्र उपकरणांची संख्या आणि सर्किट बोर्डची जागा त्यानुसार कमी केली जाईल. जसजसा उद्योग सिस्टीम लेव्हल चिप इंटिग्रेशनकडे वाटचाल करत आहे, डिझायनर उच्च RF कॉम्प्लेक्सिटी आणि लहान वायरलेस डिव्हाइसेसमध्ये दीर्घ बॅटरी आयुष्य दरम्यान विरोधाभास पूर्ण करण्यासाठी नवीन तंत्रज्ञान शोधत राहतील.

आरएफ एकत्रीकरणाची विकास स्थिती

सुमारे दोन वर्षांपूर्वी आरएफ एकत्रीकरणाचा एक महत्त्वाचा विकास दिसून आला. त्या वेळी, आरएफ तंत्रज्ञान आणि डिजिटल बेसबँड मॉडेमच्या विकासामुळे वायरलेस मोबाईल फोनमध्ये डायरेक्ट डाउन कन्व्हर्जन रिसीव्हर्ससह सुपरहिटरोडायन आरएफ डिव्हाइसेस बदलणे शक्य झाले. Superheterodyne RF साधने मल्टीस्टेज मिक्सर, फिल्टर आणि मल्टीपल व्होल्टेज कंट्रोल्ड ऑसिलेटर (VCOs) वापरतात, जे बर्याच वर्षांपासून चांगले वापरले गेले आहेत, परंतु डायरेक्ट फ्रिक्वेंसी रूपांतरण RF डिव्हाइसेसचे एकत्रीकरण GSM RF घटकांची एकूण संख्या मोठ्या प्रमाणात कमी करू शकते. १ 1990 ० च्या दशकाच्या उत्तरार्धात, साधारण सिंगल बँड सुपरहिटेरोडायन आरएफ सबसिस्टममध्ये पीए, अँटेना स्विच, एलडीओ, स्मॉल सिग्नल आरएफ आणि व्हीसीटीसीएक्सओ यांचा समावेश होता, ज्यांना सुमारे २०० स्वतंत्र उपकरणांची आवश्यकता असते; आज, आम्ही चार बँड फंक्शनसह थेट फ्रिक्वेंसी रूपांतरण प्रणालीची रचना करू शकतो, जे VCO, VCXO आणि PLL लूप फिल्टर समाकलित करते, परंतु त्याच्या घटकांची संख्या 200 पेक्षा कमी आहे. आकृती 50: उच्च एकीकरणासह चार बँड GSM ट्रान्सीव्हर.

उदाहरणार्थ, GSM साठी टेक्सास इन्स्ट्रुमेंट्सच्या ट्रान्सीव्हर trf6151 (आकृती 1) मध्ये ऑन-चिप व्होल्टेज रेग्युलेटर, VCO आणि VCO चॅनेल, PA पॉवर कंट्रोल, PLL लूप फिल्टर एज ब्लॉकर डिटेक्शन, LNA गेन स्टेप बाय स्टेप कंट्रोल आणि VCXO यांचा समावेश आहे.

डिझायनर्ससाठी, प्रगत एकत्रीकरण वायरलेस आरएफमधील काही प्रमुख समस्यांवर मात करण्यास मदत करते, त्यापैकी सर्वात मूलभूत म्हणजे डीसी वीज पुरवठा आणि ट्रान्सीव्हरचे नियमन. कॉल दरम्यान, तापमान आणि वेळ बदलून बॅटरी व्होल्टेज बदलेल. याव्यतिरिक्त, टीएक्स व्हीसीओ आणि आरएक्स व्हीसीओ वीज पुरवठ्यामधील आवाज जोडणी देखील संपूर्ण प्रणालीच्या कामगिरीवर परिणाम करेल. म्हणून, डिझायनर्सना आरएफ सर्किट बोर्ड नियामक आणि सर्वात संबंधित निष्क्रिय घटक कसे सोडवायचे या समस्येचा सामना करावा लागतो. या उपकरणांना आरएफ ट्रान्सीव्हरमध्ये समाकलित करण्याचा अर्थ असा आहे की फक्त बाह्य घटक आवश्यक आहे एक साधा डीकॉप्लिंग कॅपेसिटर, जो थेट वीज पुरवठ्याशी जोडलेला आहे, जो केवळ डिझाइन सुलभ करत नाही तर सर्किट बोर्डची जागा देखील वाचवतो.

आरएफ डिझायनर्ससाठी आणखी एक आव्हान म्हणजे व्हीसीओ ट्यूनिंग रेंज आणि लॉकिंग वेळ. सर्व एनालॉग व्हीसीओ डिझाइनमध्ये. लॉकिंग टाइम आणि ट्यूनिंग रेंजमध्ये समतोल साधणे अनेकदा आवश्यक असल्याने, लूप फिल्टर सहसा चिपच्या बाहेर ठेवला जातो. कधीकधी, हे व्हीसीओ ट्यूनिंग श्रेणीच्या सॉफ्टवेअर नियंत्रणात सोडवता येते. तथापि, ही पद्धत टेलिफोनच्या सर्वांगीण विकासासाठी अतिरिक्त संसाधनांच्या आवश्यकता पुढे ठेवते. जेव्हा डिजिटल ट्यूनिंग फंक्शन VCO मध्ये समाविष्ट केले जाते आणि सेल्फ कॅलिब्रेशन प्रदान करू शकते, तेव्हा एक विस्तारित ट्यूनिंग रेंज मिळवता येते आणि लूप फिल्टर घटक चिपमध्ये ठेवता येतो. साहजिकच, ही योजना डिझाईन अभियंत्यांना त्यांचे काम सुलभ करण्यास सक्षम करू शकते.

जीएसएम प्रणालीद्वारे आवश्यक ट्रान्समीटर पॉवर कंट्रोल प्राप्त करण्यासाठी, पीए उत्पादक साधारणपणे हे कार्य पॉवर एम्पलीफायर मॉड्यूल (पीएएम) मध्ये समाविष्ट करतात. पॉवर कंट्रोलर सहसा हजारो डिजिटल सीएमओएस गेट्सचा बनलेला असतो, जो पीएएम मधील स्वतंत्र चिपमध्ये बनविला जातो. हा घटक PAM ची किंमत US $ 0.30 ~ 0.40 ने वाढवेल. हे कार्य RF उपकरणांमध्ये समाकलित केल्याने GaAs PAM उत्पादक डिजिटल CMOS सर्किट खरेदी करू शकणार नाहीत आणि त्यांना PAM मध्ये स्थापित करू शकणार नाहीत. दरमहा हजारो उत्पादनांची निर्मिती करणाऱ्या OEM साठी, हा अनावश्यक घटक काढून टाकल्याने त्यांची किंमत मोठ्या प्रमाणात कमी होईल.

आणखी एक क्षेत्र जेथे प्रगत एकत्रीकरण भरीव बचत आणू शकते ते VCXO आहे. पूर्वी, महाग vctcxo मॉड्यूल खरेदी केले गेले आणि RF उपकरणांमध्ये स्वतंत्र घटक म्हणून डिझाइन केले गेले. म्हणूनच, vctcxo मॉड्यूलचे सामान्य घटक आरएफ उपकरणांमध्ये समाविष्ट केल्याने खर्च आणि संबंधित डिझाइन समस्या कमी होऊ शकतात. Trf6151 वापरून, vctcxo चे कार्य पूर्ण करण्यासाठी फक्त कमी किमतीचा क्रिस्टल आणि व्हॅरेक्टर आवश्यक आहे.

हे एकत्रीकरण आणि डिझाइन सरलीकरण असूनही, आरएफ डिझाइन अभियंत्यांना अजूनही कठीण पर्यायांचा सामना करावा लागतो, त्यापैकी एक इनपुट संवेदनशीलता आणि आरएक्स वीज वापर आहे. हे सर्वज्ञात आहे की कमी आवाज एम्पलीफायर (एलएनए) च्या डिझाइनमध्ये जितका मोठा प्रवाह वापरला जातो, एकूण आवाजाची वैशिष्ट्ये कमी असतात. डिझाईन इंजिनिअरने रिसीव्हरचे एकूण पॉवर बजेट आणि रिसीव्हरची संवेदनशीलता पातळी आवश्यकता निश्चित करणे आवश्यक आहे. मात्र, वीज कमी झाल्याने आवाज कमी होत नाही. खरं तर, उलट आहे. म्हणूनच, जरी ते जीएसएम मानक तपशीलाची पूर्तता करू शकते, परंतु डिझायनर्सनी स्वतःला विचारले पाहिजे की विशिष्ट संवेदनशीलता पातळी प्राप्त करण्यासाठी वीज वापरामध्ये किंमत देणे योग्य आहे का. हा प्रश्न देखील स्पष्ट करतो की डिझाइन अभियंता आणि आयसी उत्पादकांनी संपूर्ण डिझाइन प्रक्रियेत जवळून सहकार्य करणे आवश्यक का आहे. भविष्यातील आरएफ उत्पादने विकसित करताना वायरलेस उद्योगाला अधिक चांगली सेवा देण्यासाठी डिझाईन अभियंत्यांकडून अभिप्राय आयसी उत्पादकांना मार्गदर्शन करू शकतो.

एसओसीच्या दिशेने विकसित होत आहे

सिस्टम इंटिग्रेशनच्या गरजा यशस्वीरित्या पूर्ण करण्यासाठी वायरलेस सिस्टमची किंमत, शक्ती आणि जटिलता कमी करणे खूप महत्वाचे आहे. तथापि, मोबाईल फोनसाठी उच्च एकत्रीकरण समाधानाच्या विकासासाठी सेमीकंडक्टर उद्योगाला जटिल तांत्रिक अडथळे दूर करणे आवश्यक आहे. यातील काही अडथळे डिझायनर्स क्वचितच संबंधित असतात, कारण त्यापैकी अनेकांना एसओसी उपकरणे कशी बनतात हे जाणून घ्यायचे नसते, जोपर्यंत ते आवश्यक कामगिरी प्रदान करू शकते. म्हणून, काही प्रक्रिया तंत्रज्ञानाची द्रुत समज असणे आवश्यक आहे, जे सेल्युलर फोन एकत्रीकरणात वापरल्या जाणाऱ्या उपकरणांची क्षमता आणि उपलब्धता प्रभावित करेल.

मोबाईल फोन आरएफ इलेक्ट्रॉनिक प्रणालीच्या एकत्रीकरणासाठी अनेक व्यवहार्य योजना आहेत. प्रथम, पारंपारिक आरएफ आर्किटेक्चर पारंपारिक तंत्रज्ञानाचा वापर करून तुलनेने सोप्या द्विध्रुवीय किंवा बीआयसीएमओएस प्रक्रियेत लागू केले जाऊ शकते. मल्टी चिप पॅकेजिंग टेक्नॉलॉजी (सिस्टम लेव्हल पॅकेजिंग टेक्नॉलॉजी) वापरून अंतिम आरएफ चिप मोबाईल फोन डिजिटल लॉजिक फंक्शन्ससह एकत्र केली जाऊ शकते. जरी या तंत्रज्ञानाचे अनेक फायदे आहेत, जसे की परिचित आरएफ डिझाईन पद्धती आणि परिपक्व प्रक्रिया आणि तंत्रज्ञान वापरणे, चाचणी उपकरणांच्या उच्च किंमती आणि उत्पन्नामुळे व्यापारीकरण करणे कठीण आहे.

याव्यतिरिक्त, मोबाईल फोन इलेक्ट्रॉनिक प्रणालीचे एकत्रीकरण देखील प्रगत BiCMOS (SiGe) वेफर प्रक्रियेद्वारे मिळवता येते. तथापि, कारण SiGe HBT उपकरणांच्या प्रक्रियेसाठी अतिरिक्त लिथोग्राफी प्रक्रिया आवश्यक आहे, अंतिम चिपसाठी अतिरिक्त खर्च आवश्यक आहे. त्याच वेळी, कारण SiGe BiCMOS तंत्रज्ञान सर्वात प्रगत लिथोग्राफी प्रक्रिया वापरू शकत नाही, BiCMOS प्रक्रिया सहसा प्रगत डिजिटल CMOS प्रक्रियेपेक्षा मागे पडते. यामुळे मोबाईल फोनची वैशिष्ट्ये वाढवण्यासाठी आणि खर्च कमी करण्यासाठी मोठा दबाव येईल. हे साध्या वेफर प्रक्रियेच्या धोरणाने सोडवता येत नाही, कारण हे तंत्रज्ञान सिस्टम लॉजिक किंवा डिजिटल भाग प्रत्येक वेळी सर्वात कमी किंमतीत ठेवू शकत नाही. म्हणून, बीआयसीएमओएस (किंवा सीजी) मधील सिस्टम बेसबँड फंक्शन आरएफ भागाचे मोनोलिथिक एकत्रीकरण चांगली निवड नाही.

अंतिम उपाय ज्याचा विचार केला जाऊ शकतो तो CMOS मध्ये RF एकत्रीकरण आहे, ज्याला बर्याच आव्हानांचा सामना करावा लागतो. जरी अनेक सीएमओएस सेल्युलर आरएफ डिझाईन्स आहेत, या डिझाईन्स मुख्यत्वे अॅनालॉग फंक्शन्सवर आधारित आहेत. CMOS तंत्रज्ञानासह अॅनालॉग मिक्सर, फिल्टर आणि अॅम्प्लीफायर्सची अंमलबजावणी करणे कठीण आहे आणि वीज वापर सामान्यतः SiGe BiCMOS योजनेपेक्षा जास्त आहे. प्रोसेस टेक्नॉलॉजीच्या विकासासह, सीएमओएस रेटेड पातळी कमी आणि कमी होत आहे, ज्यामुळे अॅनालॉग डिझाइन अधिक कठीण होते. नवीन प्रक्रिया विकसित करण्याच्या सुरुवातीच्या टप्प्यात, डिव्हाइस मॉडेलिंग आणि प्रक्रिया परिपक्वता सामान्यतः अॅनालॉग मॉड्यूल डिझाइनसाठी आवश्यक उच्च-परिशुद्धता पॅरामीटर मॉडेलिंगची आवश्यकता पूर्ण करू शकत नाही. तथापि, अलीकडे विकसित डिजिटल CMOS RF आर्किटेक्चर मोनोलिथिक CMOS एकत्रीकरण अधिक आकर्षक बनवते.

ही सोल्यूशन्स सेमीकंडक्टर उद्योगाला चालना देतात कारण उत्पादक कमी किमतीचे आरएफ सिस्टम लेव्हल चिप सोल्यूशन्स शोधतात. जरी प्रत्येक एकत्रीकरण योजनेमध्ये अडचणी आहेत, हे खरोखर आश्चर्यकारक आहे की आरएफ घटक एकत्रीकरण इतक्या उच्च स्तरावर पोहोचू शकते. या अडचणींवर मात करून वायरलेस मोबाईल फोनच्या डिझाइनमध्ये एक मोठे पाऊल पुढे टाकले जाईल आणि नजीकच्या भविष्यात मोठ्या एकीकरणाची दिशा निश्चित केली जाईल.

या पेपरचा निष्कर्ष

आरएफ एकत्रीकरणात अजूनही अनेक अडचणी आहेत. आधुनिक मोबाईल फोनच्या प्रत्येक आरएफ डिव्हाइसला कडक कार्यक्षमतेच्या आवश्यकतांचा सामना करावा लागतो. संवेदनशीलतेची आवश्यकता सुमारे 106dbm (106 MW च्या खाली 1db) किंवा जास्त आहे आणि संबंधित स्तर फक्त काही मायक्रोव्होल्ट आहे; याव्यतिरिक्त, निवडकता, म्हणजे, उपयुक्त चॅनेलची समीप फ्रिक्वेन्सी बँड (सामान्यतः ब्लॉकिंग म्हणून ओळखली जाते) नाकारण्याची क्षमता, 60dB च्या क्रमाने असावी; याव्यतिरिक्त, सिस्टीम ऑसिलेटरला फार कमी फेजच्या आवाजाखाली ऑपरेट करणे आवश्यक आहे जेणेकरून फोल्डिंग ब्लॉकिंग एनर्जी रिसीव्हिंग बँडमध्ये येऊ नये. आरएफ एकत्रीकरण खूप कठीण आहे कारण खूप उच्च वारंवारता आणि अत्यंत कार्यक्षमतेची आवश्यकता आहे.

मल्टी फ्रिक्वेन्सी स्टँडर्डवर प्रक्रिया केल्याने संपूर्ण SOC फ्रिक्वेंसीला खरे आव्हान मिळते. बँड सिग्नल ट्रान्समिशनद्वारे निर्माण होणारी उत्तेजना कमी होईल अशी आशा आहे. डिजिटल आरएफ एकत्रीकरणाची सामग्री एका चिपमध्ये अनेक आरएफ घटक टाकण्यापेक्षा खूप जास्त आहे. हार्डवेअर शेअरिंगची नवीन रचना आवश्यक आहे.

सिस्टम डिझायनर्ससाठी, सध्याची साधी, अत्यंत एकात्मिक आणि किफायतशीर अर्धसंवाहक उपकरणे डिझाइनची जटिलता मोठ्या प्रमाणात कमी करू शकतात. त्याच वेळी, ते वायरलेस उपकरणांची वैशिष्ट्ये समृद्ध करू शकतात आणि सिस्टमचा आकार, बॅटरीचे आयुष्य आणि खर्च अपरिवर्तित ठेवू शकतात. नवीन उच्च समाकलित आरएफ उपकरणे वायरलेस डिझाइनमधील काही विवाद दूर करू शकतात आणि अभियंत्यांचा मौल्यवान वेळ वाचवू शकतात.