- 06

- Oct

ลดจำนวนส่วนประกอบและลดพื้นที่แผงวงจรผ่านการบูรณาการ RF แบบไร้สาย

ลดจำนวนส่วนประกอบและลดพื้นที่ของ แผงวงจร ผ่านการรวม RF แบบไร้สาย

ในอุปกรณ์ไร้สายในปัจจุบัน ส่วนประกอบมากกว่าครึ่งบนแผงวงจรเป็นอุปกรณ์ RF แบบแอนะล็อก ดังนั้น วิธีที่มีประสิทธิภาพในการลดพื้นที่แผงวงจรและการใช้พลังงานคือการดำเนินการรวม RF ขนาดใหญ่ขึ้น และพัฒนาไปสู่ชิประดับระบบ บทความนี้จะแนะนำสถานะการพัฒนาของการบูรณาการ RF และนำเสนอมาตรการรับมือและแนวทางแก้ไขบางประการสำหรับปัญหาเหล่านี้

ไม่กี่ปีที่ผ่านมา ตลาดโทรศัพท์มือถือถูกครอบงำโดยโทรศัพท์โหมดเดียวแบบวงเดียวและสองแบนด์ และเทคโนโลยีที่ใช้เป็นเพียง??? ถือหนึ่งหรือสองวงเซลลูลาร์ในทั้งหมด??? วิธีการมอดูเลตแบบเดียวกัน รูปแบบการเข้าถึงหลายช่องสัญญาณ และโปรโตคอลถูกนำมาใช้ในแถบความถี่พักสาย ในทางตรงกันข้าม การออกแบบโทรศัพท์มือถือรุ่นใหม่ๆ ในปัจจุบันมีความซับซ้อนกว่ามาก และสามารถให้ multi-band และ multi-mode ได้??? มีเครือข่ายบลูทูธส่วนบุคคล ตำแหน่ง GPS และฟังก์ชันอื่นๆ และฟังก์ชันการรับ UWB และทีวีก็เริ่มปรากฏขึ้น นอกจากนี้ แอปพลิเคชันต่างๆ เช่น เกม รูปภาพ เสียง และวิดีโอ ได้กลายเป็นสิ่งที่พบเห็นได้ทั่วไปในโทรศัพท์มือถือ

โทรศัพท์ไร้สายกำลังกลายเป็นอุปกรณ์ที่ซับซ้อนที่เรียกว่าศูนย์รวมความบันเทิงส่วนบุคคลแบบใช้มือถือ แนวโน้มการพัฒนายังคงสร้างความท้าทายให้กับนักออกแบบอย่างต่อเนื่อง แม้ว่าเมื่อเทียบกับโทรศัพท์มือถือที่มีฟังก์ชันเสียงเพียงอย่างเดียว โทรศัพท์มือถือรุ่นใหม่ก็เพิ่มขึ้นอย่างมากในด้านการประมวลผลการสื่อสาร การประมวลผลแอปพลิเคชัน จำนวนอินเทอร์เฟซ RF และความจุหน่วยความจำแบบบูรณาการ ผู้ใช้ยังคงคาดหวังว่าโทรศัพท์มือถือจะมีระดับเสียงที่เล็กกว่า รูปทรงเพรียวบาง ราคาและหน้าจอสีขนาดใหญ่ สามารถให้เวลาสแตนด์บายและสนทนาได้เหมือนกับโทรศัพท์ทั่วไป การรักษาขนาดโดยรวมที่มีอยู่และการใช้พลังงาน แต่การทำให้ฟังก์ชันเพิ่มขึ้นแบบทวีคูณ ในขณะที่ยังคงรักษาต้นทุนโดยรวมของระบบไว้ไม่เปลี่ยนแปลง สิ่งเหล่านี้สร้างปัญหามากมายให้กับผู้ออกแบบระบบ

เห็นได้ชัดว่า ปัญหาเกี่ยวข้องกับทุกส่วนของการออกแบบระบบทั้งหมด ตลอดจนซัพพลายเออร์ของเนื้อหาการสื่อสารและความบันเทิงไร้สายทั้งหมด พื้นที่หนึ่งที่มีประสิทธิภาพอย่างยิ่งในการลดพื้นที่บอร์ดและการใช้พลังงานคือส่วน RF ของการออกแบบระบบไร้สาย เนื่องจากในโทรศัพท์มือถือทั่วไปในปัจจุบัน ส่วนประกอบมากกว่าครึ่งบนบอร์ดเป็นส่วนประกอบ RF แบบอะนาล็อก ซึ่งรวมกันแล้วคิดเป็น 30-40% ของพื้นที่บอร์ดทั้งหมด เช่น ระบบ Bluetooth RF เช่น GPS และ WLAN ก็จะมีผลอย่างมากเช่นกัน เพิ่มข้อกำหนดสำหรับพื้นที่

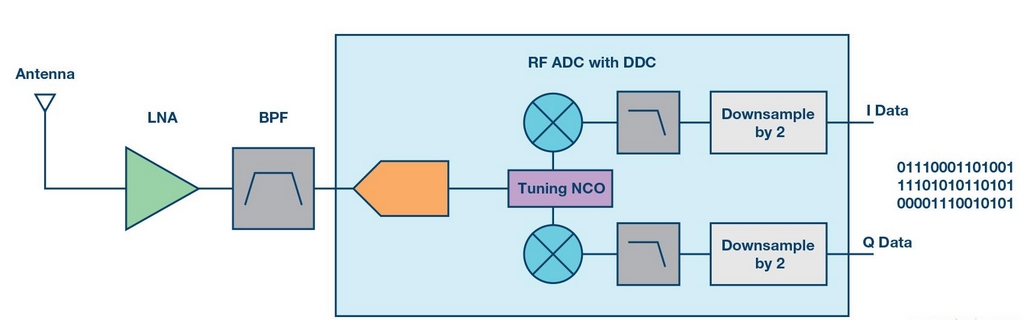

การแก้ปัญหาคือดำเนินการรวม RF ขนาดใหญ่ขึ้น และในที่สุดก็พัฒนาเป็นชิประดับระบบที่ผสานรวมอย่างสมบูรณ์ นักออกแบบบางคนใส่ตัวแปลงอนาล็อกเป็นดิจิตอลลงในเสาอากาศเพื่อลดพื้นที่แผงวงจรทั้งหมดที่จำเป็นสำหรับฟังก์ชัน RF เมื่อเทคโนโลยีการรวมเซมิคอนดักเตอร์สามารถรวมฟังก์ชันต่างๆ ได้มากขึ้นในอุปกรณ์เครื่องเดียว จำนวนอุปกรณ์ที่ไม่ต่อเนื่องและพื้นที่แผงวงจรที่ใช้เพื่อรองรับอุปกรณ์เหล่านี้จะลดลงตามไปด้วย ในขณะที่อุตสาหกรรมก้าวไปสู่การรวมชิประดับระบบ นักออกแบบจะยังคงค้นหาเทคโนโลยีใหม่ ๆ เพื่อตอบสนองความขัดแย้งระหว่างความซับซ้อนของ RF ที่สูงขึ้นและอายุการใช้งานแบตเตอรี่ที่ยาวนานขึ้นในอุปกรณ์ไร้สายขนาดเล็ก

สถานะการพัฒนาการรวม RF

การพัฒนาที่สำคัญของการรวม RF เกิดขึ้นเมื่อประมาณสองปีที่แล้ว ในขณะนั้น การพัฒนาเทคโนโลยี RF และโมเด็มเบสแบนด์ดิจิทัลทำให้สามารถเปลี่ยนอุปกรณ์ RF แบบซุปเปอร์เฮเทอโรไดน์ด้วยเครื่องรับการแปลงสัญญาณลงโดยตรงในโทรศัพท์มือถือไร้สาย อุปกรณ์ Superheterodyne RF ใช้เครื่องผสมหลายขั้นตอน ตัวกรอง และออสซิลเลเตอร์ที่ควบคุมแรงดันไฟฟ้าหลายตัว (VCO) ซึ่งใช้กันมานานหลายปี แต่การรวมอุปกรณ์ RF การแปลงความถี่โดยตรงสามารถลดจำนวนส่วนประกอบ GSM RF ทั้งหมดได้อย่างมาก ในช่วงปลายทศวรรษ 1990 ระบบย่อย RF superheterodyne แบบแถบเดียวทั่วไปรวมถึง PA, สวิตช์เสาอากาศ, LDO, RF สัญญาณขนาดเล็กและ vctcxo ซึ่งต้องใช้อุปกรณ์แยกประมาณ 200 ชิ้น; วันนี้ เราสามารถออกแบบระบบแปลงความถี่โดยตรงด้วยฟังก์ชันสี่ย่านความถี่ ซึ่งรวมตัวกรองลูป VCO, VCXO และ PLL ไว้ด้วย แต่จำนวนส่วนประกอบน้อยกว่า 50 รายการ รูปที่ 1: ตัวรับส่งสัญญาณ GSM สี่ย่านความถี่ที่มีการบูรณาการสูง

ตัวอย่างเช่น ตัวรับส่งสัญญาณ trf6151 (รูปที่ 1) ของ Texas Instruments สำหรับ GSM รวมถึงตัวควบคุมแรงดันไฟฟ้าบนชิป ช่อง VCO และ VCO การควบคุมพลังงาน PA การตรวจจับตัวบล็อกขอบตัวกรอง PLL การเพิ่ม LNA การควบคุมทีละขั้นตอนและ VCXO

สำหรับนักออกแบบ การผสานรวมขั้นสูงช่วยแก้ปัญหาหลักๆ บางอย่างใน RF ไร้สาย ซึ่งปัญหาพื้นฐานที่สุดคือแหล่งจ่ายไฟ DC และการควบคุมของตัวรับส่งสัญญาณ ระหว่างการโทร แรงดันแบตเตอรี่จะเปลี่ยนไปตามอุณหภูมิและเวลาเปลี่ยน นอกจากนี้ คัปปลิ้งสัญญาณรบกวนจากแหล่งจ่ายไฟ TX VCO และ Rx VCO จะส่งผลต่อประสิทธิภาพของทั้งระบบด้วย ดังนั้นนักออกแบบจึงต้องเผชิญกับปัญหาในการแก้ปัญหาตัวควบคุมแผงวงจร RF และส่วนประกอบแบบพาสซีฟที่เกี่ยวข้องมากที่สุด การรวมอุปกรณ์เหล่านี้เข้ากับตัวรับส่งสัญญาณ RF หมายความว่าส่วนประกอบภายนอกเท่านั้นที่จำเป็นคือตัวเก็บประจุแบบแยกส่วนอย่างง่าย ซึ่งเชื่อมต่อโดยตรงกับแหล่งจ่ายไฟ ซึ่งไม่เพียงแต่ทำให้การออกแบบง่ายขึ้น แต่ยังช่วยประหยัดพื้นที่แผงวงจรด้วย

ความท้าทายอีกประการสำหรับนักออกแบบ RF คือช่วงการปรับ VCO และเวลาในการล็อค ในการออกแบบ VCO แบบอะนาล็อกทั้งหมด เนื่องจากมักจะจำเป็นต้องปรับสมดุลเวลาล็อคและช่วงการปรับจูน ตัวกรองลูปจึงมักจะวางไว้นอกชิป บางครั้งสิ่งนี้สามารถแก้ไขได้ในการควบคุมซอฟต์แวร์ของช่วงการปรับ VCO อย่างไรก็ตาม วิธีนี้ทำให้ความต้องการทรัพยากรเพิ่มเติมสำหรับการพัฒนาโทรศัพท์โดยรวม เมื่อรวมฟังก์ชันการปรับจูนแบบดิจิตอลใน VCO และสามารถให้การสอบเทียบด้วยตนเอง สามารถรับช่วงการจูนที่ขยายได้ และวางองค์ประกอบตัวกรองลูปในชิปได้ เห็นได้ชัดว่าโครงการนี้สามารถช่วยให้วิศวกรออกแบบลดความซับซ้อนของงานได้

เพื่อให้ได้การควบคุมกำลังของเครื่องส่งสัญญาณที่ระบบ GSM ต้องการ โดยทั่วไปผู้ผลิต PA จะรวมฟังก์ชันนี้ไว้ในโมดูลเครื่องขยายเสียง (PAM) ตัวควบคุมกำลังมักจะประกอบด้วยเกท CMOS ดิจิตอลมากถึงหลายพันตัว ซึ่งผลิตขึ้นจากชิปอิสระใน PAM องค์ประกอบนี้จะเพิ่มต้นทุนของ PAM ขึ้น $0.30 ~ 0.40 ดอลลาร์สหรัฐ การรวมฟังก์ชันนี้เข้ากับอุปกรณ์ RF จะทำให้ผู้ผลิต GaAs PAM ไม่สามารถซื้อวงจร CMOS แบบดิจิทัลและติดตั้งลงใน PAM สำหรับ OEM ที่ผลิตผลิตภัณฑ์นับพันรายการทุกเดือน การนำส่วนประกอบที่ซ้ำซ้อนนี้ออกจะช่วยลดต้นทุนได้อย่างมาก

อีกด้านที่การบูรณาการขั้นสูงสามารถช่วยประหยัดค่าใช้จ่ายได้มากคือ VCXO ในอดีต โมดูล vctcxo ราคาแพงถูกซื้อและออกแบบในอุปกรณ์ RF เป็นส่วนประกอบแบบแยกส่วน ดังนั้น การรวมส่วนประกอบทั่วไปของโมดูล vctcxo เข้ากับอุปกรณ์ RF สามารถลดต้นทุนและปัญหาการออกแบบที่เกี่ยวข้องได้ การใช้ trf6151 ต้องใช้คริสตัลและวาแรคเตอร์ที่มีต้นทุนต่ำเท่านั้นเพื่อให้ฟังก์ชัน vctcxo สมบูรณ์

แม้ว่าการผสานรวมและการออกแบบให้เรียบง่ายเหล่านี้ วิศวกรออกแบบ RF ยังคงเผชิญกับตัวเลือกที่ยาก ซึ่งหนึ่งในนั้นคือความไวอินพุตและการใช้พลังงาน Rx เป็นที่ทราบกันดีว่ายิ่งกระแสที่ใช้ในการออกแบบแอมพลิฟายเออร์สัญญาณรบกวนต่ำ (LNA) มากเท่าใด ลักษณะเสียงโดยรวมก็จะยิ่งต่ำลงเท่านั้น วิศวกรออกแบบต้องกำหนดงบประมาณพลังงานทั้งหมดของเครื่องรับและข้อกำหนดระดับความไวของเครื่องรับ อย่างไรก็ตามเสียงไม่ลดลงเมื่อลดกำลังลง ในความเป็นจริงมันเป็นสิ่งที่ตรงกันข้าม ดังนั้นแม้ว่าจะสามารถเป็นไปตามข้อกำหนดมาตรฐาน GSM นักออกแบบมักจะต้องถามตัวเองว่าคุ้มค่าที่จะจ่ายราคาในการใช้พลังงานเพื่อให้ได้ระดับความไวที่แน่นอนหรือไม่ คำถามนี้ยังอธิบายว่าทำไมวิศวกรออกแบบและผู้ผลิต IC ต้องร่วมมือกันอย่างใกล้ชิดในกระบวนการออกแบบทั้งหมด คำติชมจากวิศวกรออกแบบสามารถแนะนำผู้ผลิต IC เพื่อให้บริการอุตสาหกรรมไร้สายได้ดีขึ้นเมื่อพัฒนาผลิตภัณฑ์ RF ในอนาคต

การพัฒนาสู่ SOC

การลดต้นทุน พลังงาน และความซับซ้อนของระบบไร้สายเป็นสิ่งสำคัญมากที่จะตอบสนองความต้องการของการรวมระบบได้สำเร็จ อย่างไรก็ตาม การพัฒนาโซลูชันการบูรณาการระดับสูงสำหรับโทรศัพท์มือถือต้องการให้อุตสาหกรรมเซมิคอนดักเตอร์ต้องเอาชนะอุปสรรคทางเทคนิคที่ซับซ้อน อุปสรรคบางอย่างมักไม่ค่อยเกี่ยวข้องกับนักออกแบบ เนื่องจากหลายคนไม่ต้องการทราบว่าอุปกรณ์ SOC ถูกสร้างขึ้นมาอย่างไร ตราบใดที่สามารถให้ประสิทธิภาพตามที่ต้องการได้ ดังนั้นจึงจำเป็นต้องมีความเข้าใจอย่างรวดเร็วเกี่ยวกับเทคโนโลยีกระบวนการบางอย่าง ซึ่งจะส่งผลต่อความสามารถและความพร้อมใช้งานของอุปกรณ์ที่ใช้ในการรวมโทรศัพท์มือถือ

มีแผนที่เป็นไปได้หลายประการสำหรับการรวมระบบอิเล็กทรอนิกส์ RF ของโทรศัพท์มือถือ ประการแรก สถาปัตยกรรม RF แบบดั้งเดิมสามารถนำไปใช้ในกระบวนการไบโพลาร์หรือ BiCMOS ที่ค่อนข้างง่ายโดยใช้เทคโนโลยีแบบดั้งเดิม ชิป RF สุดท้ายสามารถประกอบเข้ากับฟังก์ชันลอจิกดิจิทัลของโทรศัพท์มือถือได้โดยใช้เทคโนโลยีบรรจุภัณฑ์แบบหลายชิป (เทคโนโลยีบรรจุภัณฑ์ระดับระบบ) แม้ว่าเทคโนโลยีนี้มีข้อดีหลายประการ เช่น การใช้วิธีการออกแบบ RF ที่คุ้นเคยและกระบวนการและเทคโนโลยีที่พัฒนาเต็มที่แล้ว แต่ก็เป็นเรื่องยากที่จะนำไปใช้ในเชิงพาณิชย์ เนื่องจากอุปกรณ์ทดสอบมีราคาสูงและให้ผลผลิตสูง

นอกจากนี้ยังสามารถรวมระบบอิเล็กทรอนิกส์ของโทรศัพท์มือถือได้ด้วยกระบวนการเวเฟอร์ BiCMOS (SiGe) ขั้นสูง อย่างไรก็ตาม เนื่องจากการประมวลผลอุปกรณ์ SiGe HBT ต้องใช้กระบวนการพิมพ์หินเพิ่มเติม ชิปสุดท้ายจะต้องมีค่าใช้จ่ายเพิ่มเติม ในเวลาเดียวกัน เนื่องจากเทคโนโลยี SiGe BiCMOS ไม่สามารถใช้กระบวนการพิมพ์หินขั้นสูงได้ กระบวนการ BiCMOS มักจะล่าช้ากว่ากระบวนการ CMOS ดิจิทัลขั้นสูง สิ่งเหล่านี้จะนำมาซึ่งแรงกดดันอย่างมากในการเพิ่มคุณสมบัติของโทรศัพท์มือถือและลดต้นทุน ไม่สามารถแก้ไขได้ด้วยกลยุทธ์กระบวนการเวเฟอร์อย่างง่าย เนื่องจากเทคโนโลยีนี้ไม่สามารถรักษาตรรกะของระบบหรือชิ้นส่วนดิจิทัลให้มีราคาต่ำที่สุดได้ตลอดเวลา ดังนั้นการรวมส่วน RF ของระบบเบสแบนด์แบบเสาหินใน BiCMOS (หรือ SiGe) จึงไม่ใช่ทางเลือกที่ดี

ทางออกสุดท้ายที่พิจารณาได้คือการรวม RF ใน CMOS ซึ่งเผชิญกับความท้าทายอย่างมากเช่นกัน แม้ว่าจะมีการออกแบบ RF แบบเซลลูลาร์แบบ CMOS หลายแบบ แต่การออกแบบเหล่านี้ส่วนใหญ่ขึ้นอยู่กับฟังก์ชันแอนะล็อก เป็นเรื่องยากที่จะใช้มิกเซอร์ ฟิลเตอร์ และแอมพลิฟายเออร์แอนะล็อกร่วมกับเทคโนโลยี CMOS และการใช้พลังงานโดยทั่วไปจะมากกว่ารูปแบบ SiGe BiCMOS ด้วยการพัฒนาเทคโนโลยีกระบวนการ ระดับพิกัด CMOS ลดลงเรื่อยๆ ซึ่งทำให้การออกแบบแอนะล็อกยากขึ้น ในช่วงเริ่มต้นของการพัฒนากระบวนการใหม่ การสร้างแบบจำลองอุปกรณ์และความสมบูรณ์ของกระบวนการโดยทั่วไปไม่เป็นไปตามข้อกำหนดของการสร้างแบบจำลองพารามิเตอร์ที่มีความแม่นยำสูงที่จำเป็นสำหรับการออกแบบโมดูลแอนะล็อก อย่างไรก็ตาม สถาปัตยกรรมดิจิทัล CMOS RF ที่พัฒนาขึ้นเมื่อเร็วๆ นี้ทำให้การรวม CMOS แบบเสาหินมีความน่าสนใจยิ่งขึ้น

โซลูชั่นเหล่านี้ยังขับเคลื่อนอุตสาหกรรมเซมิคอนดักเตอร์ เนื่องจากผู้ผลิตต่างแสวงหาโซลูชั่นชิประดับระบบ RF ราคาประหยัด แม้ว่าแผนการบูรณาการแต่ละรูปแบบจะมีปัญหา แต่ก็น่าแปลกใจที่การรวมองค์ประกอบ RF สามารถบรรลุถึงระดับสูงได้ การเอาชนะปัญหาเหล่านี้จะเป็นก้าวสำคัญในการออกแบบโทรศัพท์มือถือไร้สายและกำหนดทิศทางสำหรับการบูรณาการที่ดียิ่งขึ้นในอนาคตอันใกล้

บทสรุปของบทความนี้

ยังมีปัญหามากมายในการรวม RF อุปกรณ์ RF ทุกเครื่องของโทรศัพท์มือถือสมัยใหม่ต้องเผชิญกับข้อกำหนดด้านประสิทธิภาพที่เข้มงวด ข้อกำหนดด้านความไวอยู่ที่ประมาณ – 106dbm (106db ต่ำกว่า 1 MW) หรือสูงกว่า และระดับที่สอดคล้องกันมีเพียงไม่กี่ไมโครโวลต์ นอกจากนี้ หัวกะทิ นั่นคือ ความสามารถในการปฏิเสธของช่องสัญญาณที่มีประโยชน์ไปยังแถบความถี่ที่อยู่ติดกัน (โดยทั่วไปเรียกว่าการปิดกั้น) ควรอยู่ในลำดับ 60dB; นอกจากนี้ ออสซิลเลเตอร์ของระบบจะต้องทำงานภายใต้สัญญาณรบกวนเฟสที่ต่ำมาก เพื่อป้องกันไม่ให้พลังงานที่ปิดกั้นการพับเข้าสู่แถบรับสัญญาณ การรวม RF ทำได้ยากมากเนื่องจากมีความถี่สูงมากและมีความต้องการด้านประสิทธิภาพที่สูงมาก

การประมวลผลมาตรฐานหลายความถี่นำความท้าทายที่แท้จริงมาสู่ความถี่ SOC ทั้งหมด หวังว่าจะลดการกระตุ้นที่เกิดจากการส่งสัญญาณแบบแบนด์ เนื้อหาของการรวม RF แบบดิจิทัลเป็นมากกว่าการใส่ส่วนประกอบ RF หลายตัวในชิปตัวเดียว จำเป็นต้องมีสถาปัตยกรรมใหม่ของการแบ่งปันฮาร์ดแวร์

สำหรับนักออกแบบระบบ อุปกรณ์เซมิคอนดักเตอร์ที่ใช้ง่าย ผสานรวมสูง และคุ้มค่าในปัจจุบันสามารถลดความซับซ้อนในการออกแบบได้อย่างมาก ในขณะเดียวกันก็สามารถเพิ่มคุณสมบัติของอุปกรณ์ไร้สายได้ และรักษาขนาดระบบ อายุการใช้งานแบตเตอรี่และต้นทุนให้ไม่เปลี่ยนแปลง อุปกรณ์ RF แบบบูรณาการขั้นสูงใหม่ยังสามารถขจัดข้อโต้แย้งบางประการในการออกแบบไร้สายและประหยัดเวลาอันมีค่าของวิศวกร