- 06

- 10月

通过无线射频集成减少元件数量,减少电路板面积

减少元件数量,减少面积 电路板 通过无线射频集成

在当今的无线设备中,电路板上一半以上的元件都是模拟射频设备。 因此,减少电路板面积和功耗的有效途径是进行更大规模的射频集成,向系统级芯片发展。 本文介绍了射频集成的发展现状,并针对其中一些问题提出了一些对策和解决方案。

几年前,手机市场以单频和双频单模手机为主,所用的技术只有??? 总共持有一两个蜂窝频段??? 保持频段采用相同的调制方式、多路接入方案和协议。 相比之下,今天新一代手机的设计要复杂得多,可以提供多频段和多模??? 具有蓝牙个域网、GPS定位等功能,UWB和电视接收功能也开始出现。 此外,游戏、图像、音频和视频等应用在手机中也变得非常普遍。

无线电话正在成为一种称为手持个人娱乐中心的复杂设备。 它的发展趋势不断给设计师带来更多的挑战。 尽管与仅有语音功能的手机相比,新一代手机在通信处理、应用处理、射频接口数量和集成内存容量等方面都有显着提升,但用户仍然期望手机具有更小的体积、流线型的外形、低价格实惠,彩色大显示屏,可提供类似于传统语音电话的待机和通话时间。 保持现有的整体尺寸和功耗,但使功能成倍增加,同时保持整体系统成本不变,这些都给系统设计人员带来了很多问题。

显然,问题涉及到整个系统设计的各个部分,以及所有无线通信和娱乐内容的供应商。 在减少电路板面积和功耗方面特别有效的一个领域是无线系统设计的 RF 部分。 这是因为在当今典型的手机中,板上一半以上的元件都是模拟射频元件,它们加起来占整个电路板面积的 30-40%,例如 GPS 和 WLAN 等蓝牙射频系统也将大大增加增加对空间的要求。

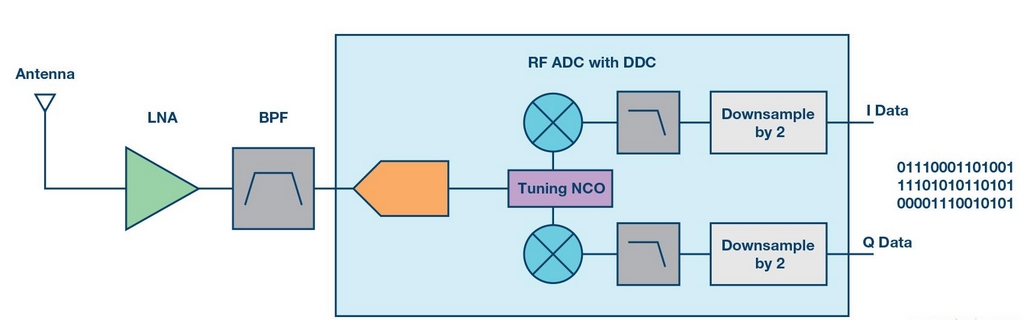

解决方案是进行更大规模的射频集成,最终发展成全集成的系统级芯片。 一些设计人员将模数转换器放入天线中,以减少射频功能所需的总电路板空间。 当半导体集成技术可以在单个器件中集成更多功能时,分立器件的数量和用于容纳这些器件的电路板空间将相应减少。 随着行业朝着系统级芯片集成的方向发展,设计人员将不断寻找新技术来解决小型无线设备中更高的 RF 复杂性和更长的电池寿命之间的矛盾。

射频集成发展现状

大约两年前出现了射频集成的重要发展。 当时,射频技术和数字基带调制解调器的发展使得在无线手机中用直接下变频接收器代替超外差射频器件成为可能。 超外差射频器件使用多级混频器、滤波器和多个压控振荡器(VCO),这些已经很好地使用了多年,但是直接变频射频器件的集成可以大大减少 GSM 射频组件的总数。 1990 年代后期,典型的单频段超外差射频子系统包括 PA、天线开关、LDO、小信号射频和 vctcxo,需要大约 200 个分立器件; 今天,我们可以设计一个具有四频段功能的直接变频系统,它集成了VCO、VCXO和PLL环路滤波器,但其元件数量不到50个。图1:高集成度的四频段GSM收发器。

例如,德州仪器 (TI) 的 GSM 收发器 trf6151(图 1)包括片上稳压器、VCO 和 VCO 通道、PA 功率控制、PLL 环路滤波器边缘阻塞检测、LNA 增益步进控制和 VCXO。

对于设计人员来说,高级集成有助于克服无线射频中的一些主要问题,其中最基本的问题是收发器的直流电源和调节。 在通话过程中,电池电压会随着温度和时间的变化而变化。 此外,TX VCO 和 Rx VCO 电源的噪声耦合也会影响整个系统的性能。 因此,设计人员面临着如何解决射频电路板稳压器和大部分相关无源元件的问题。 将这些器件集成到射频收发器中,意味着只需要一个简单的去耦电容,直接连接到电源,不仅可以简化设计,还可以节省电路板空间。

RF 设计人员面临的另一个挑战是 VCO 调谐范围和锁定时间。 在所有模拟 VCO 设计中。 因为经常需要平衡锁定时间和调谐范围,所以环路滤波器通常放置在芯片外部。 有时,这可以通过 VCO 调谐范围的软件控制来解决。 但是,这种方式对电话的整体发展提出了额外的资源需求。 当VCO中包含数字调谐功能并且可以提供自校准时,可以获得扩展的调谐范围,并且可以在芯片中放置环路滤波器元件。 显然,这种方案可以让设计工程师简化他们的工作。

为了获得GSM系统所需的发射机功率控制,PA厂商一般都在功率放大器模块(PAM)中包含了这个功能。 电源控制器通常由多达数千个数字 CMOS 门组成,这些门在 PAM 中制作在一个独立的芯片中。 该要素将使 PAM 的成本增加 0.30 美元~0.40 美元。 将此功能集成到 RF 设备中将使 GaAs PAM 制造商无需购买数字 CMOS 电路并将其安装到 PAM 中。 对于每月生产数千种产品的 OEM 而言,移除这个冗余组件将大大降低其成本。

高级集成可以带来大量节省的另一个领域是 VCXO。 过去,昂贵的 vctcxo 模块是在 RF 设备中作为分立元件购买和设计的。 因此,将 vctcxo 模块的通用组件集成到 RF 设备中可以降低成本和相关的设计问题。 使用trf6151,只需要一个低成本的晶振和变容二极管就可以完成vctcxo的功能。

尽管有这些集成和设计简化,RF 设计工程师仍然面临艰难的选择,其中之一是输入灵敏度和 Rx 功耗。 众所周知,低噪声放大器(LNA)设计中使用的电流越大,整体噪声特性越低。 设计工程师必须确定接收器的总功率预算和接收器的灵敏度等级要求。 但是,噪声不会随着功率的降低而降低。 事实上,情况恰恰相反。 因此,虽然它可以满足GSM标准规范,但设计人员必须经常问自己是否值得为达到一定的灵敏度水平而在功耗上付出代价。 这个问题也解释了为什么设计工程师和IC制造商在整个设计过程中需要密切合作。 设计工程师的反馈可以指导 IC 制造商在开发未来的射频产品时更好地服务于无线行业。

向SOC发展

降低无线系统的成本、功耗和复杂性对于成功满足系统集成的要求非常重要。 然而,开发手机高集成度解决方案需要半导体行业克服复杂的技术障碍。 其中一些障碍很少为设计人员所关注,因为他们中的许多人并不想知道 SOC 器件是如何制造的,只要它能够提供所需的性能即可。 因此,有必要快速了解一些工艺技术,这些技术会影响手机集成中使用的设备的能力和可用性。

手机射频电子系统的集成有几种可行的方案。 首先,可以使用传统技术在相对简单的双极或 BiCMOS 工艺中实现传统的 RF 架构。 最终的射频芯片可以使用多芯片封装技术(系统级封装技术)与手机数字逻辑功能组装在一起。 虽然这项技术有很多优点,例如使用熟悉的射频设计方法和成熟的工艺和技术,但由于测试设备的成本和良率较高,很难商业化。

此外,手机电子系统的集成也可以通过先进的BiCMOS(SiGe)晶圆工艺获得。 然而,由于 SiGe HBT 器件的加工需要额外的光刻工艺,最终的芯片将需要额外的成本。 同时,由于SiGe BiCMOS工艺无法使用最先进的光刻工艺,BiCMOS工艺通常落后于先进的数字CMOS工艺。 这些都会给手机增加特性和降低成本带来巨大压力。 它无法通过简单的晶圆工艺策略解决,因为该技术无法始终将系统逻辑或数字部分保持在尽可能低的价格。 因此,将系统基带功能射频部分单片集成在 BiCMOS(或 SiGe)中并不是一个好的选择。

可以考虑的最终解决方案是 CMOS 中的 RF 集成,这也面临着相当大的挑战。 尽管有多种 CMOS 蜂窝射频设计,但这些设计主要基于模拟功能。 CMOS技术难以实现模拟混频器、滤波器和放大器,功耗一般大于SiGe BiCMOS方案。 随着工艺技术的发展,CMOS的额定等级越来越低,这使得模拟设计变得更加困难。 在开发新工艺的初期,器件建模和工艺成熟度一般不能满足模拟模块设计所需的高精度参数建模要求。 然而,最近开发的数字 CMOS RF 架构使单片 CMOS 集成更具吸引力。

随着制造商寻求低成本射频系统级芯片解决方案,这些解决方案也推动了半导体行业的发展。 虽然每种集成方案都有难度,但射频元件集成度能达到如此高的水平,确实令人惊讶。 克服这些困难将使无线手机的设计向前迈出一大步,并为不久的将来更大程度的集成指明方向。

本文结论

RF集成还存在很多困难。 现代手机的每个射频设备都面临着严格的性能要求。 灵敏度要求约为–106dbm(106MW以下1db)或更高,对应的电平只有几微伏; 另外,选择性,即有用信道对相邻频段的抑制能力(俗称阻塞),应在60dB左右; 此外,系统振荡器需要在极低的相位噪声下工作,以防止折叠阻塞能量进入接收频带。 由于频率非常高且性能要求极其苛刻,因此射频集成非常困难。

处理多频率标准给整个SOC频率带来了真正的挑战。 希望减少带内信号传输产生的激励。 数字射频集成的内容远不止将多个射频组件放在一个芯片中。 需要一种新的硬件共享架构。

对于系统设计人员来说,目前简单、高度集成且具有成本效益的半导体器件可以大大降低设计复杂度。 同时,它们可以丰富无线设备的特性,保持系统尺寸、电池寿命和成本不变。 新的高度集成的射频器件还可以消除无线设计中的一些争议,节省工程师的宝贵时间。