- 05

- Oct

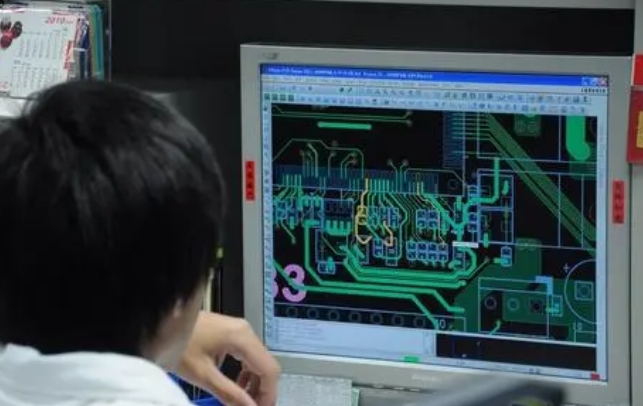

पीसीबी उत्पादन डिजाइन के छह सारांश

के छह सारांश पीसीबी उत्पादन डिज़ाइन

1. लेआउट

सबसे पहले, पीसीबी के आकार पर विचार करें। जब पीसीबी सर्किट बोर्ड का आकार बहुत बड़ा होता है, तो मुद्रित लाइन लंबी होती है, प्रतिबाधा बढ़ जाती है, शोर-रोधी क्षमता कम हो जाती है और लागत बढ़ जाती है; यदि यह बहुत छोटा है, तो गर्मी अपव्यय खराब है, और आसन्न रेखाएं आसानी से परेशान हो सकती हैं। पीसीबी का आकार निर्धारित करने के बाद, विशेष घटकों की स्थिति निर्धारित करें। अंत में, सर्किट के सभी घटकों को सर्किट की कार्यात्मक इकाइयों के अनुसार व्यवस्थित किया जाता है।

विशेष तत्वों की स्थिति का निर्धारण करते समय निम्नलिखित सिद्धांतों का पालन किया जाना चाहिए:

(१) उच्च-आवृत्ति घटकों के बीच तारों को यथासंभव छोटा करें, और उनके वितरण मापदंडों और पारस्परिक विद्युत चुम्बकीय हस्तक्षेप को कम करने का प्रयास करें। हस्तक्षेप के लिए अतिसंवेदनशील घटक एक दूसरे के बहुत करीब नहीं होने चाहिए, और इनपुट और आउटपुट घटक जितना संभव हो उतना दूर होना चाहिए।

(२) कुछ घटकों या तारों के बीच उच्च संभावित अंतर हो सकता है, इसलिए डिस्चार्ज के कारण होने वाले आकस्मिक शॉर्ट सर्किट से बचने के लिए उनके बीच की दूरी बढ़ाई जानी चाहिए। उच्च वोल्टेज वाले घटकों को उन स्थानों पर व्यवस्थित किया जाएगा जहां कमीशनिंग के दौरान स्पर्श करना आसान नहीं है।

(३) मुद्रित प्लेट के पोजिशनिंग होल और निश्चित समर्थन द्वारा कब्जा कर लिया गया स्थान आरक्षित किया जाएगा।

सर्किट की कार्यात्मक इकाई के अनुसार, सर्किट के सभी घटकों का लेआउट निम्नलिखित सिद्धांतों का पालन करेगा:

(१) प्रत्येक कार्यात्मक सर्किट इकाई की स्थिति को सर्किट प्रवाह के अनुसार व्यवस्थित करें, लेआउट को सिग्नल प्रवाह के लिए सुविधाजनक बनाएं, और जहां तक संभव हो सिग्नल को उसी दिशा में रखें।

(२) प्रत्येक कार्यात्मक सर्किट के मुख्य घटकों को केंद्र और उसके चारों ओर लेआउट के रूप में लें। घटकों को पीसीबी पर समान रूप से, बड़े करीने से और कॉम्पैक्ट रूप से व्यवस्थित किया जाना चाहिए। जहां तक संभव हो घटकों के बीच लीड और कनेक्शन को कम और छोटा किया जाएगा।

(३) उच्च आवृत्ति पर काम करने वाले सर्किट के लिए, घटकों के बीच वितरण मापदंडों पर विचार किया जाना चाहिए। सामान्य परिपथों के लिए, घटकों को यथासंभव समानांतर में व्यवस्थित किया जाएगा। इस तरह, यह न केवल सुंदर है, बल्कि इकट्ठा करना और वेल्ड करना आसान है, और बड़े पैमाने पर उत्पादन करना आसान है।

(४) सर्किट बोर्ड के किनारे पर स्थित घटक आमतौर पर सर्किट बोर्ड के किनारे से २ मिमी से कम दूर नहीं होते हैं। सर्किट बोर्ड का सबसे अच्छा आकार आयत है। पहलू अनुपात 4:2 से 3:2 है। जब सर्किट बोर्ड की सतह का आकार 4×3 मिमी से अधिक हो, तो सर्किट बोर्ड की यांत्रिक शक्ति पर विचार किया जाएगा।

2. तारों

तारों के सिद्धांत इस प्रकार हैं:

(१) इनपुट और आउटपुट टर्मिनलों पर उपयोग किए जाने वाले कंडक्टर जहां तक संभव हो आसन्न समानांतर से बचना चाहिए। फीडबैक कपलिंग से बचने के लिए लाइनों के बीच ग्राउंड वायर जोड़ना बेहतर है।

(२) मुद्रित कंडक्टर की न्यूनतम चौड़ाई मुख्य रूप से कंडक्टर और इंसुलेटिंग बेस प्लेट के बीच आसंजन शक्ति और उनके माध्यम से बहने वाली धारा द्वारा निर्धारित की जाती है।

(३) मुद्रित तार का मोड़ आम तौर पर गोलाकार चाप होता है, और समकोण या सम्मिलित कोण उच्च आवृत्ति सर्किट में विद्युत प्रदर्शन को प्रभावित करेगा। इसके अलावा, बड़े क्षेत्र की तांबे की पन्नी के उपयोग से बचने की कोशिश करें, अन्यथा, लंबे समय तक गर्म होने पर तांबे की पन्नी का विस्तार और गिरना आसान होता है। जब तांबे की पन्नी के एक बड़े क्षेत्र का उपयोग किया जाना चाहिए, तो ग्रिड आकार का उपयोग करना सबसे अच्छा है, जो तांबे की पन्नी और सब्सट्रेट के बीच चिपकने वाले के गर्म होने से उत्पन्न वाष्पशील गैस को खत्म करने के लिए अनुकूल है।

3. पाद

पैड सेंटर होल (इन-लाइन डिवाइस) डिवाइस के लीड व्यास से थोड़ा बड़ा होता है। यदि पैड बहुत बड़ा है, तो झूठी सोल्डरिंग बनाना आसान है। पैड का बाहरी व्यास डी आमतौर पर (डी + 1.2) मिमी से कम नहीं होता है, जहां डी लीड होल व्यास होता है। उच्च घनत्व वाले डिजिटल सर्किट के लिए, पैड का न्यूनतम व्यास (डी + 1.0) मिमी हो सकता है।

पीसीबी और सर्किट के लिए विरोधी हस्तक्षेप उपाय:

मुद्रित सर्किट बोर्ड का हस्तक्षेप-विरोधी डिज़ाइन विशिष्ट सर्किट से निकटता से संबंधित है। यहां, पीसीबी विरोधी हस्तक्षेप डिजाइन के कुछ सामान्य उपायों का वर्णन किया गया है।

1. पावर कॉर्ड डिजाइन

मुद्रित सर्किट बोर्ड की धारा के अनुसार, बिजली लाइन की चौड़ाई बढ़ाने और लूप प्रतिरोध को कम करने का प्रयास करें। साथ ही, बिजली लाइन और ग्राउंड वायर की दिशा को डेटा ट्रांसमिशन की दिशा के अनुरूप बनाएं, जो शोर विरोधी क्षमता को बढ़ाने में मदद करता है।

2. लॉट डिजाइन

ग्राउंड वायर डिजाइन के सिद्धांत हैं:

(१) डिजिटल और एनालॉग को अलग किया जाता है। यदि सर्किट बोर्ड पर लॉजिक सर्किट और लीनियर सर्किट दोनों हैं, तो उन्हें यथासंभव अलग किया जाना चाहिए। जहां तक संभव हो कम आवृत्ति वाले सर्किट की ग्राउंडिंग के लिए सिंगल पॉइंट पैरेलल ग्राउंडिंग को अपनाया जाएगा। यदि वास्तविक वायरिंग को जोड़ना मुश्किल है, तो इसे आंशिक रूप से श्रृंखला में जोड़ा जा सकता है और फिर समानांतर में जोड़ा जा सकता है। हाई-फ़्रीक्वेंसी सर्किट के लिए मल्टी पॉइंट सीरीज़ ग्राउंडिंग को अपनाया जाएगा, ग्राउंड वायर को छोटा और किराए पर लिया जाएगा, और जहां तक संभव हो हाई-फ़्रीक्वेंसी घटकों के आसपास बड़े क्षेत्र के ग्राउंड फ़ॉइल जैसे ग्रिड का उपयोग किया जाएगा।

(२) ग्राउंडिंग तार जितना संभव हो उतना मोटा होना चाहिए। यदि ग्राउंडिंग वायर सिलने वाले तार से बना है, तो ग्राउंडिंग पोटेंशियल करंट के परिवर्तन के साथ बदल जाता है, जिससे कि एंटी नॉइज़ परफॉर्मेंस कम हो जाती है। इसलिए ग्राउंडिंग वायर को मोटा किया जाना चाहिए ताकि वह प्रिंटेड बोर्ड पर स्वीकार्य करंट से तीन गुना ज्यादा गुजर सके। यदि संभव हो तो, ग्राउंडिंग तार 2 ~ 2 मिमी से अधिक होना चाहिए।

(३) ग्राउंडिंग वायर एक बंद लूप बनाता है। केवल डिजिटल सर्किट से बने मुद्रित बोर्डों के लिए, ग्राउंडिंग सर्किट को क्लस्टर लूप में व्यवस्थित किया जाता है, जो शोर-रोधी क्षमता में सुधार कर सकता है।

4. संधारित्र विन्यास को कम करना

पीसीबी डिजाइन के पारंपरिक तरीकों में से एक पीसीबी के प्रत्येक प्रमुख भाग पर उपयुक्त डिकूपिंग कैपेसिटर को कॉन्फ़िगर करना है। संधारित्र को अलग करने का सामान्य विन्यास सिद्धांत है:

(1) पावर इनपुट टर्मिनल 10 ~ 100uF इलेक्ट्रोलाइटिक कैपेसिटर से जुड़ा है। यदि संभव हो, तो 100uF से अधिक कनेक्ट करना बेहतर है।

(2) सिद्धांत रूप में, प्रत्येक एकीकृत सर्किट चिप 0.01uF ~ 0.1uF सिरेमिक चिप कैपेसिटर से लैस होगा। मुद्रित बोर्ड में अपर्याप्त अंतराल के मामले में, प्रत्येक 1 ~ 10 चिप्स में 4 ~ 8PF संधारित्र की व्यवस्था की जा सकती है।

(३) शटडाउन के दौरान कमजोर शोर प्रतिरोध और बड़े बिजली परिवर्तन वाले उपकरणों के लिए, जैसे कि रैम और रोम स्टोरेज डिवाइस, डिकूपिंग कैपेसिटर को चिप की पावर लाइन और ग्राउंड वायर के बीच सीधे जोड़ा जाएगा।

5. छेद डिजाइन के माध्यम से

हाई-स्पीड पीसीबी डिज़ाइन में, प्रतीत होता है कि साधारण विअस अक्सर सर्किट डिज़ाइन पर बहुत नकारात्मक प्रभाव डालते हैं। वायस के परजीवी प्रभावों के कारण होने वाले प्रतिकूल प्रभावों को कम करने के लिए, हम डिजाइन में अपना सर्वश्रेष्ठ प्रयास कर सकते हैं

(१) लागत और सिग्नल की गुणवत्ता को ध्यान में रखते हुए, आकार के माध्यम से एक उचित चयन किया जाता है। उदाहरण के लिए, 1-6 लेयर मेमोरी मॉड्यूल PCB डिज़ाइन के लिए, 10/10MIL (ड्रिलिंग / पैड) वायस का चयन करना बेहतर है। कुछ उच्च-घनत्व वाले छोटे आकार के बोर्डों के लिए, आप 20 / 8mil vias का उपयोग करने का भी प्रयास कर सकते हैं। वर्तमान तकनीकी परिस्थितियों में, छेद के माध्यम से छोटे का उपयोग करना मुश्किल है (जब छेद की गहराई ड्रिलिंग व्यास के 18 गुना से अधिक हो, तो यह सुनिश्चित करना असंभव है कि छेद की दीवार को तांबे के साथ समान रूप से चढ़ाया जा सकता है); शक्ति या जमीन के व्यास के लिए, प्रतिबाधा को कम करने के लिए बड़े आकार पर विचार किया जा सकता है

(२) पीसीबी बोर्ड पर सिग्नल रूटिंग जहाँ तक संभव हो परतों को नहीं बदलेगा, अर्थात जहाँ तक संभव हो अनावश्यक वायस का उपयोग नहीं किया जाएगा

(३) बिजली की आपूर्ति और जमीन के पिन पास में छिद्रित होने चाहिए। वाया और पिन के बीच की लीड जितनी कम होगी, उतना ही बेहतर होगा

(४) सिग्नल के लिए निकटतम सर्किट प्रदान करने के लिए सिग्नल लेयर चेंज के वायस के पास कुछ ग्राउंडेड वायस रखें। आप पीसीबी पर बड़ी संख्या में अनावश्यक ग्राउंडिंग विअस भी रख सकते हैं

6. शोर और विद्युत चुम्बकीय हस्तक्षेप को कम करने में कुछ अनुभव

(१) यदि आप कम गति वाले चिप्स का उपयोग कर सकते हैं, तो आपको उच्च गति वाले चिप्स की आवश्यकता नहीं है। हाई-स्पीड चिप्स का उपयोग प्रमुख स्थानों पर किया जाता है

(२) नियंत्रण सर्किट के ऊपरी और निचले किनारों की कूद दर को कम करने के लिए प्रतिरोधों की एक श्रृंखला का उपयोग किया जा सकता है।

(३) रिले आदि के लिए किसी प्रकार की भिगोना प्रदान करने का प्रयास करें, जैसे कि RC वर्तमान भिगोना सेट करना

(४) सबसे कम आवृत्ति वाली घड़ी का उपयोग करें जो सिस्टम की आवश्यकताओं को पूरा करती हो।

(५) घड़ी का उपयोग करने वाले उपकरण के लिए घड़ी यथासंभव करीब होनी चाहिए। क्वार्ट्ज क्रिस्टल थरथरानवाला के खोल को आधार बनाया जाएगा। क्लॉक एरिया ग्राउंड वायर से घिरा होना चाहिए। घड़ी की रेखा यथासंभव छोटी होनी चाहिए। क्वार्ट्ज क्रिस्टल के नीचे और शोर संवेदनशील डिवाइस के नीचे कोई वायरिंग नहीं होनी चाहिए। घड़ी, बस और चिप चयन सिग्नल I/O लाइन और कनेक्टर से बहुत दूर होंगे। I / O रेखा के लंबवत घड़ी की रेखा का हस्तक्षेप I / O रेखा के समानांतर से कम है

(६) अप्रयुक्त गेट सर्किट के इनपुट एंड को निलंबित नहीं किया जाएगा, अप्रयुक्त परिचालन एम्पलीफायर के सकारात्मक इनपुट एंड को ग्राउंड किया जाएगा, और नेगेटिव इनपुट एंड को आउटपुट एंड से जोड़ा जाएगा