- 05

- Oct

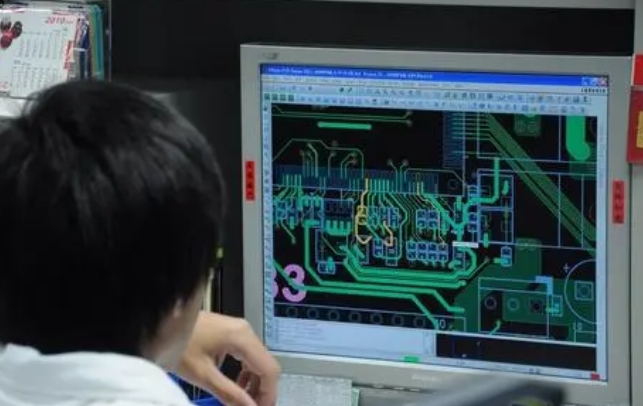

PCB ထုတ်လုပ်မှုဒီဇိုင်းအကျဉ်းချုပ်ခြောက်ချက်

အကျဉ်းချုပ်ခြောက်ချက် PCB ထုတ်လုပ်မှုဒီဇိုင်း

၁

ပထမ ဦး စွာ PCB ၏အရွယ်အစားကိုစဉ်းစားပါ။ PCB ဆားကစ်ဘုတ်၏အရွယ်အစားသည်အလွန်ကြီးလာသောအခါပုံနှိပ်ထားသောလိုင်းသည်ရှည်လျားလာသည်။ ၎င်းသည်သေးငယ်ပါကအပူဖြန့်ဝေမှုသည်ညံ့ဖျင်းပြီးအနီးအနားရှိလိုင်းများသည်အနှောင့်အယှက်ဖြစ်လွယ်သည်။ PCB ၏အရွယ်အစားကိုဆုံးဖြတ်ပြီးနောက်အထူးအစိတ်အပိုင်းများ၏တည်နေရာကိုဆုံးဖြတ်ပါ။ နောက်ဆုံးတွင်ဆားကစ်၏အစိတ်အပိုင်းအားလုံးကိုဆားကစ်၏အလုပ်လုပ်နိုင်သောယူနစ်များအတိုင်းစီစဉ်ပေးသည်။

အထူးအစိတ်အပိုင်းများ၏တည်နေရာကိုဆုံးဖြတ်ရာတွင်အောက်ပါအခြေခံမူများကိုသတိပြုရမည်။

(၁) ကြိမ်နှုန်းမြင့်အစိတ်အပိုင်းများအကြားဝါယာကြိုးများကိုအတတ်နိုင်ဆုံးတိုစေ။ ၎င်းတို့၏ဖြန့်ဖြူးသတ်မှတ်ချက်များနှင့်အပြန်အလှန်လျှပ်စစ်သံလိုက်စွက်ဖက်မှုကိုလျှော့ချရန်ကြိုးစားပါ။ အနှောင့်အယှက်ဖြစ်စေနိုင်သောအစိတ်အပိုင်းများသည်တစ်ခုနှင့်တစ်ခုအလွန်နီးကပ်မှုမရှိစေဘဲအ ၀ င်အထွက်နှင့်အစိတ်အပိုင်းများကိုတတ်နိုင်သမျှဝေးဝေးထားပါ။

(၂) အချို့အစိတ်အပိုင်းများသို့မဟုတ်ဝိုင်ယာများအကြားအလားအလာကွာခြားချက်မြင့်မားသည်၊ ထို့ကြောင့်ထုတ်လွှတ်မှုကြောင့်မတော်တဆဝါယာရှော့မဖြစ်စေရန်၎င်းတို့နှစ်ခုကြားအကွာအဝေးကိုတိုးသင့်သည်။ ဗို့အားမြင့်သောအစိတ်အပိုင်းများကို commissioning လုပ်နေစဉ်ထိရန်မလွယ်ကူသောနေရာများတွင်စီစဉ်ပေးရမည်။

(၃) ပုံနှိပ်ပန်းကန်၏နေရာအပေါက်နေရာယူထားသောနေရာနှင့်ပုံသေထောက်ခံမှုကိုရယူထားရမည်။

ဆားကစ်၏အလုပ်လုပ်နိုင်သောယူနစ်အရ circuit ၏အစိတ်အပိုင်းအားလုံး၏အပြင်အဆင်သည်အောက်ပါအခြေခံမူများနှင့်အညီလိုက်နာရမည်။

(၁) ဆားကစ်စီးဆင်းမှုအတိုင်းအလုပ်လုပ်တဲ့ဆားကစ်ယူနစ်တစ်ခုစီရဲ့တည်နေရာကိုစီစဉ်ပါ၊ အချက်ပြစီးဆင်းမှုအတွက်အဆင်ပြေစေမယ့်အပြင်အချက်ပြကိုတတ်နိုင်သမျှတူညီတဲ့ ဦး တည်ချက်အတိုင်းထားပါ။

(၂) လည်ပတ်မှုပတ်လမ်းတစ်ခုစီ၏အဓိကအစိတ်အပိုင်းများကိုအလယ်ဗဟိုနှင့်အပြင်အဆင်အဖြစ်ယူပါ။ အစိတ်အပိုင်းများကို PCB ပေါ်တွင်အညီအမျှ၊ သပ်ရပ်စွာ၊ ကျစ်လစ်သိပ်သည်းစွာစီစဉ်ရမည်။ အစိတ်အပိုင်းများအကြားဆက်သွယ်မှုများနှင့်ဆက်သွယ်မှုများကိုအတတ်နိုင်ဆုံးအတိုချုံ့ပြီးလျှော့ချရမည်။

(၃) ကြိမ်နှုန်းမြင့်သောဆားကစ်အတွက်အစိတ်အပိုင်းများအကြားဖြန့်ဖြူးရေးကိုထည့်သွင်းစဉ်းစားသင့်သည်။ ယေဘူယျဆားကစ်များအတွက်အစိတ်အပိုင်းများကိုအတတ်နိုင်ဆုံးပြိုင်တူစီစဉ်ပေးရမည်။ ဤနည်းအားဖြင့်၎င်းသည်လှပရုံသာမကစုဝေးရန်နှင့်ပေါင်းရန်လွယ်ကူပြီးအစုလိုက်အပြုံလိုက်ထုတ်လုပ်ရန်လွယ်ကူသည်။

(၄) ဆားကစ်ဘုတ်၏အစွန်းတွင်ရှိသောအစိတ်အပိုင်းများသည်များသောအားဖြင့်ဆားကစ်ဘုတ်၏အစွန်းမှ ၂ မီလီမီတာထက်မပိုပါ။ ဆားကစ်ဘုတ်၏အကောင်းဆုံးပုံသဏ္ာန်သည်စတုဂံဖြစ်သည်။ မြင်ကွင်းအချိုးသည် ၃: ၂ မှ ၄: ၃ ဖြစ်သည်။ ဆားကစ်ဘုတ်၏မျက်နှာပြင်အရွယ်အစားသည် ၂၀၀x၁၅၀ မီလီမီတာထက်ကြီးလျှင်ဆားကစ်ဘုတ်၏စက်ပိုင်းဆိုင်ရာအားကိုထည့်သွင်းစဉ်းစားရမည်။

၅

ဝါယာကြိုး၏အခြေခံမူများမှာအောက်ပါအတိုင်းဖြစ်သည်။

(၁) အဝင်နှင့်အထွက် terminal များတွင်အသုံးပြုသော conductors များသည်ဘေးချင်းယှဉ်ပြိုင်ခြင်းကိုတတ်နိုင်သမျှရှောင်ကြဉ်ရမည်။ တုံ့ပြန်မှုဆက်နွယ်မှုကိုရှောင်ရှားရန်လိုင်းများကြားတွင်မြေဝါယာကြိုးများထည့်ခြင်းသည်ပိုကောင်းသည်။

(၂) ပုံနှိပ်စပယ်ယာ၏အနိမ့်ဆုံးအကျယ်ကို conductor နှင့် insulating base plate နှင့်၎င်းတို့မှတဆင့်စီးဆင်းသောလက်ရှိကော်ကြားခိုင်ခံ့မှုတို့ဖြင့်အဓိကဆုံးဖြတ်သည်။

(၃) ပုံနှိပ်ထားသောဝါယာကြိုး၏အကွေးသည်ယေဘုယျအားဖြင့်စက်ဝိုင်းပုံစံဖြစ်ပြီး၊ ညာဘက်ထောင့်သို့မဟုတ်ပါ ၀ င်သောထောင့်သည်ကြိမ်နှုန်းမြင့်ဆားကစ်တွင်လျှပ်စစ်စွမ်းဆောင်ရည်ကိုထိခိုက်စေလိမ့်မည်။ ထို့အပြင်၊ ကြေးနီသတ္တုပြားများချဲ့ခြင်းနှင့်ပြုတ်ကျခြင်းတို့သည်အချိန်ကြာမြင့်စွာအပူခံရသောအခါဖြစ်ပေါ်လွယ်သည်။ ကြေးနီသတ္တုပြားကိုဧရိယာကြီးကြီးမားမားအသုံးပြုရသောအခါကြေးနီသတ္တုပြားနှင့်အောက်ခံအကြားကော်များမှအပူဓာတ်ထုတ်ပေးသောမတည်ငြိမ်သောဓာတ်ငွေ့များကိုဖယ်ရှားပစ်ရန်အကောင်းဆုံးဖြစ်သည်။

၃

pad အလယ်အပေါက် (in-line device) သည် device lead diameter ထက်အနည်းငယ်ပိုကြီးသည်။ pad သည်ကြီးလွန်းလျှင်အတုဂဟေပြုလုပ်ရန်လွယ်ကူသည်။ Pad ၏အပြင်ဘက်အချင်းသည်ယေဘူယျအားဖြင့် (D + 1.2) mm ထက်နည်းပြီး D သည်ခဲပေါက်အချင်းဖြစ်သည်။ သိပ်သည်းဆမြင့်မားသောဒစ်ဂျစ်တယ်ဆားကစ်များအတွက် pad ၏အနိမ့်ဆုံးအချင်းသည် (D + 1.0) မီလီမီတာဖြစ်နိုင်သည်။

PCB နှင့် circuit အတွက်ဆန့်ကျင်သောစွက်ဖက်မှုအစီအမံများ

ပုံနှိပ်ဆားကစ်ဘုတ်၏အနှောင့်အယှက်ကိုဆန့်ကျင်သောဒီဇိုင်းသည်တိကျသောပတ်လမ်းနှင့်နီးစပ်သည်။ ဤတွင် PCB ဆန့်ကျင်စွက်ဖက်မှုဆန့်ကျင်ရေးဒီဇိုင်း၏အသုံးများသောအစီအမံအချို့ကိုသာဖော်ပြထားသည်။

1. ပါဝါကြိုးဒီဇိုင်း

ပုံနှိပ်တိုက်နယ်ဘုတ်၏လက်ရှိအခြေအနေအရဓာတ်အားလိုင်းအကျယ်ကိုတိုးရန်နှင့်ကွင်းခုခံမှုကိုလျှော့ချရန်ကြိုးစားပါ။ တစ်ချိန်တည်းမှာပင်ဓာတ်အားလိုင်းနှင့်မြေဝါယာကြိုး၏ ဦး တည်ချက်သည်အသံလှိုင်းဆန့်ကျင်နိုင်စွမ်းကိုမြှင့်တင်ရန်ကူညီပေးသည်။

2. အများကြီးဒီဇိုင်း

မြေဝါယာကြိုးဒီဇိုင်း၏အခြေခံမူများမှာ

(၁) ဒစ်ဂျစ်တယ်နှင့် analog ကိုခွဲခြားထားသည်။ ဆားကစ်ဘုတ်တွင် logic circuit များနှင့် linear circuits နှစ်ခုလုံးရှိလျှင်၎င်းတို့ကိုတတ်နိုင်သမျှခွဲထားရမည်။ ကြိမ်နှုန်းအနိမ့်ပတ်လမ်း၏မြေစိုက်အားအတွက်အတတ်နိုင်ဆုံး Single point parallel grounding ကိုလက်ခံရလိမ့်မည်။ အမှန်တကယ်ဝိုင်ယာကြိုးများချိတ်ဆက်ရန်ခက်ခဲလျှင်၎င်းကိုတစ်စိတ်တစ်ပိုင်းအား series များနှင့်ချိတ်ဆက်နိုင်ပြီး၎င်းအားအပြိုင်ချိတ်ဆက်နိုင်သည်။ ကြိမ်နှုန်းမြင့်ကြိမ်နှုန်းအတွက် multi point series grounding ကိုလက်ခံရလိမ့်မည်၊ မြေဝါယာကြိုးတိုတိုနှင့်ငှားရမည်၊ ဧရိယာကျယ်မြေစိုက်သတ္တုပြားကဲ့သို့ကြိမ်နှုန်းမြင့်အစိတ်အပိုင်းများကိုအတတ်နိုင်ဆုံးအသုံးပြုရမည်။

(၂) မြေစိုက်ကြိုးသည်အတတ်နိုင်ဆုံးအထူရှိရမည်။ အကယ်၍ grounding wire ကိုချုပ်ထားသောဝါယာကြိုးဖြင့်ပြုလုပ်လျှင် anti -noise စွမ်းဆောင်ရည်ကိုလျော့ကျစေသောကြောင့် current ပြောင်းလဲခြင်းနှင့်အတူ grounding အလားအလာသည်ပြောင်းလဲသွားသည်။ ထို့ကြောင့်မြေစိုက်ဝါယာကြိုးသည်၎င်းကိုပုံနှိပ်ဘုတ်တွင်သုံးနိုင်သောသုံးဆဖြတ်သွားနိုင်စေရန်ထူသင့်သည်။ ဖြစ်နိုင်လျှင် grounding wire သည် ၂ ~ ၃ မီလီမီတာထက်ပိုရမည်။

(၃) မြေပြင်ဝါယာကြိုးသည်ပိတ်ထားသောကွင်းတစ်ခုဖြစ်သည်။ ဒစ်ဂျစ်တယ်ဆားကစ်များဖြင့်သာဖွဲ့စည်းထားသောပုံနှိပ်ပျဉ်ပြားများအတွက် grounding circuit ကို anti ဆူညံသံစွမ်းရည်ကိုတိုးတက်စေနိုင်သော cluster loop တွင်စီစဉ်ပေးထားသည်။

4. Decoupling capacitor ဖွဲ့စည်းတည်ဆောက်ပုံ

PCB ဒီဇိုင်း၏သမားရိုးကျနည်းလမ်းများအနက်တစ်ခုမှာ PCB ၏သော့ချက်အစိတ်အပိုင်းတစ်ခုစီ၌သင့်လျော်သော decoupling capacitors များကို configure လုပ်ရန်ဖြစ်သည်။ decoupling capacitor ၏ယေဘူယျဖွဲ့စည်းတည်ဆောက်ပုံအခြေခံမူမှာ

(၁) power input terminal ကို 1 ~ 10uF electrolytic capacitor နှင့်ချိတ်ဆက်ထားသည်။ ဖြစ်နိုင်လျှင် 100uF ထက်ပိုချိတ်ဆက်တာပိုကောင်းပါတယ်။

(၂) မူအရပေါင်းစည်းထားသော circuit chip တစ်ခုစီကို 2uF ~ 0.01uF ceramic chip capacitor တပ်ဆင်ထားရမည်။ ပုံနှိပ်ဘုတ်တွင်ကွက်လပ်မလုံလောက်ပါက 0.1 ~ 1 ချစ်ပ်တိုင်း 10-4PF capacitor ကိုစီစဉ်နိုင်သည်။

(၃) RAM နှင့် ROM သိုလှောင်မှုကဲ့သို့အားနည်းသောဆူညံသံခုခံမှုများနှင့်ပိတ်ပစ်နေစဉ်ကြီးမားသောပါဝါပြောင်းလဲမှုရှိသောကိရိယာများအတွက် decoupling capacitors များကိုဓာတ်အားလိုင်းနှင့်ချစ်ပ်၏မြေဝါယာကြိုးများအကြားတိုက်ရိုက်ဆက်သွယ်ရမည်။

5. အပေါက်ဒီဇိုင်းအားဖြင့်

မြန်နှုန်းမြင့် PCB ဒီဇိုင်းတွင်ထင်ရသောရိုးရှင်းသောအရာများသည်ဆားကစ်ဒီဇိုင်းအတွက်ကြီးမားသောအနုတ်လက္ခဏာသက်ရောက်မှုများဖြစ်ပေါ်စေတတ်သည်။ မြင်ကွင်းများ၏ကပ်ပါးသက်ရောက်မှုများကြောင့်ဖြစ်ပေါ်လာသောဆိုးရွားသောသက်ရောက်မှုများကိုလျှော့ချနိုင်ရန်ဒီဇိုင်းကိုအကောင်းဆုံးကြိုးစားနိုင်သည်။

(၁) ကုန်ကျစရိတ်နှင့်အချက်ပြအရည်အသွေးတို့ကိုထည့်သွင်းစဉ်း စား၍ သင့်တော်သောအရွယ်အစားကိုရွေးချယ်သည်။ ဥပမာအားဖြင့် ၆-၁၀ အလွှာ memory module PCB ဒီဇိုင်းအတွက် 1 / 6MIL (drilling / pad) vias များကိုရွေးတာပိုကောင်းပါတယ်။ အချို့သောသိပ်သည်းဆမြင့်မားသောသေးငယ်သည့်ဘုတ်များအတွက် 10 / 10mil vias ကိုသုံးရန်ကြိုးစားနိုင်သည်။ လက်ရှိနည်းပညာအခြေအနေများအရ၎င်းသည်တွင်းငယ်များကိုအသုံးပြုရန်ခက်ခဲသည် (တွင်း၏အတိမ်အနက်သည်တူးဖော်သည့်အချင်း ၆ ဆထက်ကျော်လွန်ပါကတွင်းနံရံအားကြေးနီဖြင့်တစ်ထပ်တည်းကျအောင်ပြုလုပ်ရန်သေချာရန်မဖြစ်နိုင်ပေ) ပါဝါ (သို့) မြေပြင်အတွက်ပိုမိုကြီးမားသောအရွယ်အစားသည် impedance ကိုလျှော့ချရန်စဉ်းစားနိုင်သည်

(၂) PCB board ပေါ်တွင်အချက်ပြလမ်းကြောင်းများအလွှာများကိုတတ်နိုင်သမျှမပြောင်းရ၊ ဆိုလိုသည်မှာမလိုအပ်သောနေရာများကိုတတ်နိုင်သမျှအသုံးမပြုရပါ။

(၃) ပါဝါထောက်ပံ့ရေးနှင့်မြေစိုက်တံများကိုအနီးအနားတွင်ဖောက်ထားသင့်သည်။ တဆင့်နှင့်တပင်ကြားအကြားပိုတိုလေပိုကောင်းလေဖြစ်သည်

(၄) အချက်ပြအတွက်အနီးဆုံးပတ် ၀ န်းကျင်ကိုအချက်ပြအလွှာပြောင်းရန်အချက်အလွှာများအနီးရှိနေရာအချို့ကိုနေရာချပါ။ သင်မလိုအပ်သော grounding Vias များစွာကို PCB ပေါ်တွင်ပင်ထားနိုင်သည်

၆။ အချို့သောဆူညံသံများနှင့်လျှပ်စစ်သံလိုက်နှောင့်ယှက်မှုများကိုလျှော့ချရာတွင်အတွေ့အကြုံရှိသည်

(၁) သင်မြန်နှုန်းနိမ့်ချစ်ပ်များကိုသုံးနိုင်လျှင်မြန်နှုန်းမြင့်ပြားများမလိုပါ။ မြန်နှုန်းမြင့်ချစ်ပ်များကိုအဓိကနေရာများတွင်အသုံးပြုသည်

(၂) control circuit ၏အပေါ်နှင့်အောက်အနားခုန်နှုန်းကိုလျှော့ချရန် resistors များကို series တစ်ခုတွင်သုံးနိုင်သည်။

(၃) RC damping ကဲ့သို့သော relay များအတွက် damping ပုံစံအချို့ကိုပေးရန်ကြိုးစားပါ

(၄) စနစ်လိုအပ်ချက်နှင့်အညီအနိမ့်ဆုံးကြိမ်နှုန်းနာရီကိုသုံးပါ။

(၅) နာရီသည်နာရီကို သုံး၍ ကိရိယာနှင့်အတတ်နိုင်ဆုံးနီးကပ်စေရမည်။ quartz crystal oscillator ၏အခွံကိုမြေစိုက်ရမည်။ နာရီဧရိယာကိုမြေဝါယာကြိုးဖြင့်ဝန်းရံရမည်။ နာရီလိုင်းကိုအတတ်နိုင်ဆုံးတိုစေရမည်။ ကျောက်သလင်းကျောက်သလင်းအောက်တွင်နှင့်သံဆူညံသံအာရုံခံကိရိယာအောက်တွင်ဝါယာကြိုးများမရှိစေရ။ နာရီ၊ ဘတ်စ်ကားနှင့်ချစ်ပ်ရွေးချယ်မှုအချက်ပြများသည် I / O လိုင်းနှင့်ချိတ်ဆက်မှုနှင့်ဝေးရပါမည်။ I / O line မှ perpendicular clock line ၏စွက်ဖက်မှုသည် I / O line နှင့်အပြိုင်နည်းသည်

(၆) အသုံးမ ၀ င်သောတံခါးပတ်လမ်းကြောင်း၏အဆုံးကိုဆိုင်းငံ့ထားမည်မဟုတ်၊ အသုံးမ ၀ င်သောလည်ပတ်မှုအသံချဲ့စက်၏အပြုသဘောပါ ၀ င်မှုအဆုံးသည်မြေပြင်နှင့်အနုတ်လက္ခဏာအ ၀ င်အဆုံးကိုအထွက်အထွက်သို့ဆက်သွယ်လိမ့်မည်။