- 22

- Sep

Kiểm soát quy trình sản xuất chính cho bo mạch PCB cấp cao

Kiểm soát quy trình sản xuất chính cho Cấp cao PCB bảng

Bảng mạch nhà cao tầng được định nghĩa chung là bảng mạch nhiều tầng cao từ 10 – 20 tầng trở lên, khó gia công hơn so với bảng mạch truyền thống. bảng mạch nhiều lớp và có yêu cầu về chất lượng và độ tin cậy cao. Nó chủ yếu được sử dụng trong thiết bị truyền thông, máy chủ cao cấp, điện tử y tế, hàng không, điều khiển công nghiệp, quân sự và các lĩnh vực khác. Trong những năm gần đây, nhu cầu thị trường về ván cao tầng trong lĩnh vực truyền thông ứng dụng, trạm gốc, hàng không và quân sự vẫn rất mạnh. Với sự phát triển nhanh chóng của thị trường thiết bị viễn thông Trung Quốc, triển vọng thị trường ván cao tầng là đầy hứa hẹn.

Hiện nay, Nhà sản xuất PCBNhững cơ sở có thể sản xuất hàng loạt PCB cao tầng ở Trung Quốc chủ yếu đến từ các doanh nghiệp có vốn đầu tư nước ngoài hoặc một số doanh nghiệp trong nước. Việc sản xuất PCB cao tầng không chỉ đòi hỏi đầu tư công nghệ, thiết bị cao hơn mà còn cần sự tích lũy kinh nghiệm của các cán bộ kỹ thuật và nhân viên sản xuất. Đồng thời, thủ tục chứng nhận nhập khẩu PCB cao tầng của khách hàng rất khắt khe và rườm rà. Do đó, ngưỡng để PCB cao vào doanh nghiệp là cao và chu kỳ sản xuất công nghiệp hóa kéo dài. Số lớp PCB trung bình đã trở thành một chỉ số kỹ thuật quan trọng để đo lường trình độ kỹ thuật và cơ cấu sản phẩm của các doanh nghiệp có PCB. Bài báo này mô tả ngắn gọn những khó khăn xử lý chính gặp phải trong quá trình sản xuất PCB cao tầng và giới thiệu các điểm kiểm soát chính của các quy trình sản xuất chính của PCB cao tầng để bạn tham khảo.

1 、 Khó khăn sản xuất chính

So với các đặc điểm của các sản phẩm bảng mạch thông thường, bảng mạch cao tầng có các đặc điểm của bảng dày hơn, nhiều lớp hơn, đường và vias dày đặc hơn, kích thước đơn vị lớn hơn, lớp điện môi mỏng hơn và yêu cầu khắt khe hơn về không gian bên trong, căn chỉnh lớp xen kẽ, kiểm soát trở kháng và độ tin cậy.

1.1 khó khăn trong việc căn chỉnh lớp xen kẽ

Do số lượng lớn các lớp bảng mạch cao tầng, thiết kế của khách hàng ngày càng có yêu cầu khắt khe về việc căn chỉnh các lớp PCB và dung sai căn chỉnh giữa các lớp thường được kiểm soát đến ± 75 μm. Xem xét thiết kế kích thước đơn vị lớn của bảng mạch cao tầng, nhiệt độ và độ ẩm môi trường xung quanh xưởng truyền đồ họa, sự chồng chất lệch vị trí và chế độ định vị lớp xen kẽ gây ra bởi sự mở rộng và co lại không nhất quán của các lớp bảng lõi khác nhau, khó kiểm soát lớp xen kẽ hơn sự liên kết của bảng cao tầng.

1.2 khó khăn khi làm mạch bên trong

Bo mạch cao tầng sử dụng các vật liệu đặc biệt như Tg cao, tốc độ cao, tần số cao, đồng dày và lớp điện môi mỏng, đặt ra các yêu cầu cao về chế tạo và kiểm soát kích thước đồ họa của mạch bên trong, chẳng hạn như tính toàn vẹn của tín hiệu trở kháng truyền dẫn, làm tăng độ khó của việc chế tạo mạch bên trong. Chiều rộng dòng và khoảng cách dòng nhỏ, độ hở và ngắn mạch tăng lên, độ ngắn vi mô tăng lên và tỷ lệ đạt yêu cầu thấp; Có nhiều lớp tín hiệu của các đường mảnh, và xác suất phát hiện thiếu AOI ở lớp bên trong tăng lên; Tấm lõi bên trong mỏng, dễ gấp lại dẫn đến độ tiếp xúc kém, sau khi khắc rất dễ bị cuộn lại; Hầu hết các loại ván cao tầng là ván hệ thống có kích thước đơn vị lớn, giá thành phế liệu thành phẩm tương đối cao.

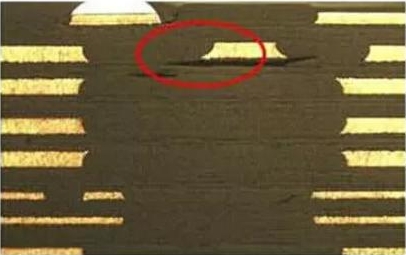

1.3 khó khăn bức xúc trong sản xuất

Khi nhiều tấm lõi bên trong và các tấm bán bảo dưỡng được xếp chồng lên nhau, các khuyết tật như tấm trượt, tách lớp, khoang nhựa và cặn bong bóng rất dễ xảy ra trong quá trình sản xuất uốn nếp. Khi thiết kế kết cấu ép phải xem xét đầy đủ khả năng chịu nhiệt, chịu điện áp, lượng keo đổ đầy và độ dày trung bình của vật liệu, từ đó đề ra chương trình ép tấm cao tầng hợp lý. Có nhiều lớp, và việc kiểm soát sự giãn nở và co lại và sự bù trừ của hệ số kích thước không thể nhất quán; Lớp cách điện giữa các lớp mỏng, dễ dẫn đến việc không đạt yêu cầu trong thử nghiệm độ tin cậy của lớp xen kẽ. Hình 1 là sơ đồ khuyết tật của sự phân tách tấm vỡ sau thử nghiệm ứng suất nhiệt.

Fig.1

1.4 khó khăn khi khoan

Việc sử dụng các tấm đồng đặc biệt Tg cao, tốc độ cao, tần số cao và đồng dày làm tăng độ khó khi khoan nhám, khoan gờ và khoan loại bỏ bụi bẩn. Có nhiều lớp, tổng chiều dày đồng và chiều dày tấm được tích tụ, và dụng cụ khoan dễ bị phá vỡ; Sự cố quán cà phê do BGA dày đặc và khoảng cách tường lỗ hẹp; Do độ dày của tấm nên dễ gây ra hiện tượng khoan xiên.

2 、 Kiểm soát quy trình sản xuất chính

2.1 lựa chọn vật liệu

Với sự phát triển của linh kiện điện tử theo hướng hiệu suất cao, đa chức năng, đồng thời mang đến khả năng truyền tín hiệu tần số cao và tốc độ cao. Do đó, đòi hỏi hằng số điện môi và tổn thất điện môi của vật liệu mạch điện tử phải tương đối thấp, cũng như CTE thấp, độ hấp thụ nước thấp và vật liệu đồng mạ đồng hiệu suất cao tốt hơn, để đáp ứng các yêu cầu xử lý và độ tin cậy cao. -sao ban. Các nhà cung cấp tấm thông thường chủ yếu bao gồm loạt, B, C và D. Xem Bảng 1 để so sánh các đặc điểm chính của bốn chất nền bên trong này. Đối với bảng mạch đồng dày cao tầng, tấm bán bảo dưỡng có hàm lượng nhựa cao được chọn. Lượng keo chảy của tấm bán bảo dưỡng liên lớp đủ để lấp đầy hình họa lớp bên trong. Nếu lớp trung gian cách nhiệt quá dày, ván thành phẩm rất dễ quá dày. Ngược lại, nếu lớp trung gian cách điện quá mỏng sẽ dễ gây ra các vấn đề về chất lượng như phân tầng trung áp, thử cao áp không đạt yêu cầu. Vì vậy, việc lựa chọn vật liệu làm trung gian cách nhiệt là rất quan trọng.

2.2 thiết kế cấu trúc nhiều lớp

Các yếu tố chính được xem xét khi thiết kế cấu trúc nhiều lớp là khả năng chịu nhiệt, điện áp, lượng keo lấp đầy và độ dày lớp điện môi của vật liệu và các nguyên tắc chính sau đây phải được tuân thủ.

(1) Nhà sản xuất tấm và tấm cốt lõi bán bảo dưỡng phải nhất quán. Để đảm bảo độ tin cậy của PCB, không nên sử dụng một tấm 1080 hoặc 106 bán bảo dưỡng cho tất cả các lớp của tấm bán bảo dưỡng (trừ khi khách hàng có yêu cầu đặc biệt). Khi khách hàng không có yêu cầu về độ dày trung bình, độ dày trung bình giữa các lớp phải được đảm bảo ≥ 0.09mm theo ipc-a-600g.

(2) Khi khách hàng yêu cầu ván Tg cao, ván lõi và tấm bán bảo dưỡng sẽ sử dụng vật liệu Tg cao tương ứng.

(3) Đối với lớp nền bên trong 3oz trở lên, hãy chọn tấm bán bảo dưỡng có hàm lượng nhựa cao, chẳng hạn như 1080r / C65%, 1080hr / C 68%, 106R / C 73%, 106hr / C76%; Tuy nhiên, phải tránh thiết kế cấu trúc của tất cả 106 tấm nửa đóng rắn bằng keo cao càng tốt để ngăn chặn sự chồng chất của nhiều tấm 106 nửa đã đóng rắn. Bởi vì sợi thủy tinh quá mỏng, sợi thủy tinh bị sụp đổ trong diện tích bề mặt lớn, ảnh hưởng đến sự ổn định kích thước và sự tách lớp nổ tấm.

(4) Nếu khách hàng không có yêu cầu đặc biệt, dung sai độ dày của lớp điện môi xen kẽ thường được kiểm soát bằng + / – 10%. Đối với tấm trở kháng, dung sai độ dày điện môi được kiểm soát bởi dung sai ipc-4101 C / M. Nếu yếu tố ảnh hưởng trở kháng có liên quan đến độ dày của đế, thì dung sai của tấm cũng phải được kiểm soát bằng dung sai ipc-4101 C / M.

2.3 điều khiển căn chỉnh xen kẽ

Để có độ chính xác của việc bù kích thước bảng lõi bên trong và kiểm soát kích thước sản xuất, cần phải bù chính xác kích thước đồ họa của từng lớp bảng cao tầng thông qua dữ liệu và dữ liệu lịch sử kinh nghiệm được thu thập trong quá trình sản xuất trong một thời gian nhất định để đảm bảo tính nhất quán của sự giãn nở và co lại của từng lớp ván lõi. Chọn chế độ định vị lớp xen kẽ có độ chính xác cao và đáng tin cậy trước khi ép, chẳng hạn như ghim Lam, kết hợp nóng chảy và đinh tán. Thiết lập quy trình ép thích hợp và bảo trì máy ép hàng ngày là chìa khóa để đảm bảo chất lượng ép, kiểm soát keo ép và hiệu quả làm mát, đồng thời giảm thiểu sự cố lệch lớp giữa các lớp. Việc kiểm soát sự liên kết giữa các lớp cần được xem xét một cách toàn diện từ các yếu tố như giá trị bù lớp bên trong, chế độ định vị ép, các thông số quá trình ép, đặc tính vật liệu, v.v.

2.4 quy trình dòng bên trong

Vì khả năng phân tích của máy phơi sáng truyền thống nhỏ hơn 50 μ M. để sản xuất tấm cao tầng, máy ảnh trực tiếp laser (LDI) có thể được giới thiệu để cải thiện khả năng phân tích đồ họa, có thể đạt tới 20 μM hoặc hơn. Độ chính xác căn chỉnh của máy phơi sáng truyền thống là ± 25 μ m. Độ chính xác căn chỉnh giữa các lớp lớn hơn 50 μ m。 Sử dụng máy phơi sáng căn chỉnh chính xác cao, độ chính xác căn chỉnh đồ họa có thể được cải thiện lên 15 μ M, kiểm soát độ chính xác căn chỉnh giữa các lớp 30 μ M, giúp giảm độ lệch căn chỉnh của thiết bị truyền thống và cải thiện độ chính xác liên kết giữa các lớp của tấm sàn cao tầng.

Để cải thiện khả năng ăn mòn của đường dây, cần phải đưa ra mức bù thích hợp cho chiều rộng của đường và miếng đệm (hoặc vòng hàn) trong thiết kế kỹ thuật, cũng như xem xét thiết kế chi tiết hơn đối với lượng bù đặc biệt. đồ họa, chẳng hạn như dòng trả về và dòng độc lập. Xác nhận xem phần bù thiết kế của chiều rộng đường trong, khoảng cách đường, kích thước vòng cách ly, đường độc lập và khoảng cách lỗ đến đường là hợp lý hay không, nếu không hãy thay đổi thiết kế kỹ thuật. Có các yêu cầu thiết kế trở kháng và điện kháng cảm ứng. Chú ý đến việc bù thiết kế của đường dây độc lập và đường dây trở kháng có đủ hay không. Kiểm soát các thông số trong quá trình khắc. Sản xuất hàng loạt chỉ có thể được thực hiện sau khi mảnh đầu tiên được xác nhận là đủ tiêu chuẩn. Để giảm ăn mòn bên ăn mòn, cần phải kiểm soát thành phần hóa học của từng nhóm dung dịch ăn mòn trong phạm vi tốt nhất. Thiết bị dây chuyền khắc truyền thống không đủ công suất khắc. Thiết bị có thể được chuyển đổi kỹ thuật hoặc nhập khẩu vào thiết bị dây chuyền khắc có độ chính xác cao để cải thiện tính đồng nhất của quá trình khắc và giảm các vấn đề như cạnh thô và khắc không sạch.

2.5 quá trình ép

Hiện nay, các phương pháp định vị lớp xen kẽ trước khi ép chủ yếu bao gồm: ghim Lam, nung nóng, đinh tán, kết hợp giữa nung nóng và đinh tán. Các phương pháp định vị khác nhau được áp dụng cho các cấu trúc sản phẩm khác nhau. Đối với sàn nhà cao tầng, phương pháp định vị bốn rãnh (chốt Lam) hoặc phương pháp hợp nhất + tán đinh sẽ được sử dụng. Máy đột lỗ hoạt động phải đục lỗ định vị và độ chính xác đột lỗ phải được kiểm soát trong phạm vi ± 25 μ m。 Trong quá trình nung chảy, tia X sẽ được sử dụng để kiểm tra độ lệch lớp của tấm đầu tiên được thực hiện bởi máy điều chỉnh và lô chỉ có thể được thực hiện sau khi độ lệch lớp đủ điều kiện. Trong quá trình sản xuất hàng loạt, cần phải kiểm tra xem từng tấm có bị nóng chảy vào bộ phận hay không để ngăn chặn sự tách lớp tiếp theo. Thiết bị ép sử dụng máy ép hỗ trợ hiệu suất cao để đáp ứng độ chính xác và độ tin cậy của căn chỉnh giữa các lớp của các tấm cao tầng.

Theo cấu trúc nhiều lớp của bảng mạch cao tầng và vật liệu được sử dụng, hãy nghiên cứu quy trình ép thích hợp, đặt tốc độ tăng nhiệt độ tốt nhất và đường cong, giảm tốc độ tăng nhiệt độ của bảng mạch ép một cách thích hợp trong quy trình ép bảng mạch nhiều lớp thông thường, kéo dài thời gian đóng rắn ở nhiệt độ cao, làm cho nhựa chảy hoàn toàn và đông đặc, đồng thời tránh các vấn đề như trượt tấm và lệch lớp xen kẽ trong quá trình ép. Các tấm có giá trị TG khác nhau không thể giống tấm ghi; Các tấm có các thông số thông thường không được trộn lẫn với các tấm có các thông số đặc biệt; Để đảm bảo tính hợp lý của hệ số co giãn và giãn nở đã cho, các đặc tính của các tấm khác nhau và các tấm bán bảo dưỡng là khác nhau, do đó, các thông số tấm tương ứng của tấm được đóng rắn bán phần cần được ép và các thông số quá trình cần được xác minh đối với các vật liệu đặc biệt có chưa bao giờ được sử dụng.

2.6 quá trình khoan

Do quá dày của tấm và lớp đồng gây ra bởi sự chồng chất của từng lớp, mũi khoan bị mòn nghiêm trọng và rất dễ bị gãy mũi khoan. Số lượng lỗ, tốc độ rơi và tốc độ quay phải được giảm một cách thích hợp. Đo chính xác sự giãn nở và co lại của tấm để cung cấp hệ số chính xác; Nếu số lớp ≥ 14, đường kính lỗ ≤ 0.2mm hoặc khoảng cách từ lỗ đến đường ≤ 0.175mm thì sử dụng máy khoan có độ chính xác vị trí lỗ ≤ 0.025mm để sản xuất; đường kính φ Đường kính lỗ trên 4.0mm sử dụng khoan từng bước và tỷ lệ đường kính độ dày là 12: 1. Nó được sản xuất bằng cách khoan từng bước và khoan tích cực và tiêu cực; Kiểm soát độ dày của gờ và lỗ khoan. Sàn nhà cao tầng phải được khoan bằng dao khoan mới hoặc dao khoan mài càng xa càng tốt, và độ dày lỗ phải được kiểm soát trong phạm vi 25um. Để cải thiện vấn đề lỗ khoan của tấm đồng dày cao tầng, thông qua xác minh hàng loạt, việc sử dụng tấm nền mật độ cao, số lượng tấm nhiều lớp là một và thời gian mài của mũi khoan được kiểm soát trong vòng 3 lần, mà có thể cải thiện hiệu quả gờ khoan

Đối với bảng cao tầng được sử dụng cho tần số cao, tốc độ cao và truyền dữ liệu lớn, công nghệ khoan ngược là một phương pháp hiệu quả để cải thiện tính toàn vẹn của tín hiệu. Việc khoan sau chủ yếu kiểm soát chiều dài cuống còn lại, độ nhất quán vị trí lỗ của hai lỗ khoan và dây đồng trong lỗ. Không phải thiết bị máy khoan nào cũng có chức năng khoan ngược, vì vậy cần nâng cấp thiết bị máy khoan (có chức năng khoan ngược) hoặc mua máy khoan có chức năng khoan ngược. Công nghệ khoan ngược được áp dụng từ các tài liệu liên quan đến ngành và sản xuất hàng loạt trưởng thành chủ yếu bao gồm: phương pháp khoan ngược điều khiển độ sâu truyền thống, khoan ngược với lớp phản hồi tín hiệu ở lớp trong và tính toán độ sâu khoan ngược theo tỷ lệ chiều dày tấm. Nó sẽ không được lặp lại ở đây.

3 、 Kiểm tra độ tin cậy

Bo mạch cao tầng nói chung là một tấm hệ thống, dày và nặng hơn tấm nhiều lớp thông thường, có kích thước đơn vị lớn hơn, và nhiệt dung tương ứng cũng lớn hơn. Trong quá trình hàn, cần nhiều nhiệt hơn và thời gian hàn ở nhiệt độ cao kéo dài. Ở 217 ℃ (điểm nóng chảy của đồng thiếc bạc hàn), mất 50 giây đến 90 giây. Đồng thời, tốc độ nguội của tấm cao tầng tương đối chậm nên thời gian thử nghiệm nung chảy lại kéo dài. Kết hợp với các tiêu chuẩn ipc-6012c, IPC-TM-650 và các yêu cầu công nghiệp, thử nghiệm độ tin cậy chính của bo mạch cao tầng được thực hiện.