- 05

- Oct

Verduidelik die vliegtoets van die printplaat in detail

Verduidelik die vliegtoets van circuit board in detail

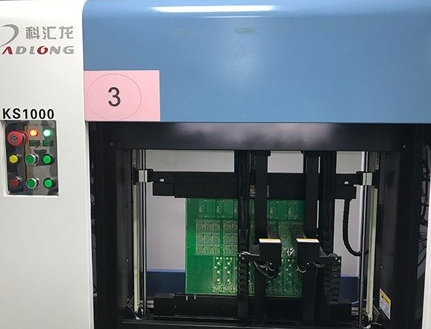

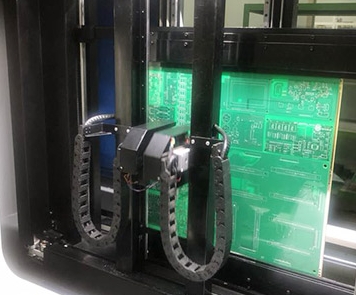

Die beginsel van die toets van die bordplank is baie eenvoudig. Dit benodig slegs twee sondes om x, y en Z te beweeg om die twee ente van elke stroombaan een vir een te toets, dus is dit nie nodig om nog ‘n duur toestel te maak nie. As gevolg van die eindpunttoets, is die metingsnelheid egter baie stadig, ongeveer 10 ~ 40 punte / sekonde, dus dit is meer geskik vir monsters en klein massaproduksie; Wat die testdigtheid betref, kan ‘n vliegnaaldtoets toegepas word op planke met ‘n baie hoë digtheid, soos MCM.

Beginsel van vliegnaaldtoetser: dit is om vier sondes te gebruik om hoëspanningsisolasie en ‘n lae weerstandstoetsingstoets (toets die oop kring en kortsluiting van die lyn) vir die printplaat uit te voer, solank die toetsdokument bestaan uit die die oorspronklike kliënt en ons ontwerp -ontwerp.

Na die toets is daar vier redes vir kortsluiting en oop kring:

1. Klante -lêer: die toetser kan slegs vergelyk, nie ontleed nie

2. Produksie lyn produksie: warpage, soldeer weerstand en nie-standaard karakters van PCB bord

3. Omskakeling van verwerkingsdata: ons onderneming neem die ontwerp -ontwerp -toets aan, en sommige data (via) van die ingenieursontwerp word weggelaat

4. Toerustingfaktore: sagteware en hardeware probleme

Toe ons die bord ontvang wat ons toets geslaag het en dit geplak het, het ons ‘n gat in die gat gekry. Ek weet nie wat dit veroorsaak het nie. Ons het verkeerdelik gedink dit is ons toets, maar dit is ook gestuur. Daar is trouens baie redes vir die deurblokkade.

Daar is vier redes hiervoor:

1. Gebreke wat veroorsaak word deur boor: die plaat is gemaak van glasvezel van epoksiedhars. Na die boor is daar stof in die gat wat nie skoongemaak word nie, en koper kan nie na die uitharding neergelê word nie. Oor die algemeen toets ons dit in die skakel met die vliegnaald.

2. Gebreke wat veroorsaak word deur koperneerslag: die koperneersettingstyd is te kort, die gatkoper is nie vol nie, en die kopergat is nie vol wanneer tin toegedien word nie, wat lei tot swak toestande. (in chemiese koperafsetting is daar ‘n probleem met die verwydering van gomslak, die verwydering van alkaliese olie, mikro -ets, aktivering, versnelling en koperneerslag, eindelose ontwikkeling, oormatige ets, en die oorblywende oplossing in die gat word nie skoon gewas nie. Spesifieke skakels word breedvoerig ontleed)

3. Kaarte op die printplaat benodig te veel stroom en word nie vooraf ingelig oor die noodsaaklikheid om die gatkoper te verdik nie. Hierdie probleem kom dikwels voor wanneer die stroom te groot is om die gatkoper te smelt nadat dit aangeskakel is. Die stroom van die teoretiese waarde is nie eweredig aan die werklike stroom nie, wat lei tot die direkte smelting van die gatkoper na aanskakeling, wat lei tot die nie -kontinuïteit van die via, wat verkeerdelik vermoed word dat die toets nie uitgevoer is nie.

4. Gebreke wat veroorsaak word deur die kwaliteit en tegnologie van SMT -blik: die lang verblyf tyd in die blikoond tydens sweiswerk lei tot die smelt van gatkoper, wat tot defekte lei. Beginnervennote is nie baie akkuraat in die beoordeling van die materiaal in terme van beheertyd nie, en maak foute onder die materiaal by hoë temperatuur, wat lei tot die mislukking van koper smelt. Die huidige plaatfabriek kan basies die vliegnaaldtoets op die monsters doen, dus as die plaat nog steeds ‘n 100% vliegnaaldtoets moet vind om probleme in die hande van die bord te vermy.

Gevolgtrekking: deur te leer, sal ons meer weet oor die klein besonderhede van die vliegnaaldtoets en weet waarheen ons moet gaan.